Материалы по тегу: cpu

|

15.12.2023 [00:30], Алексей Степин

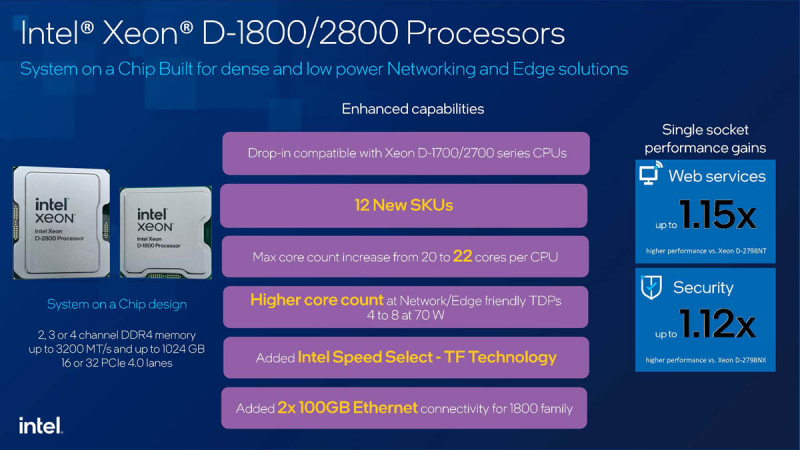

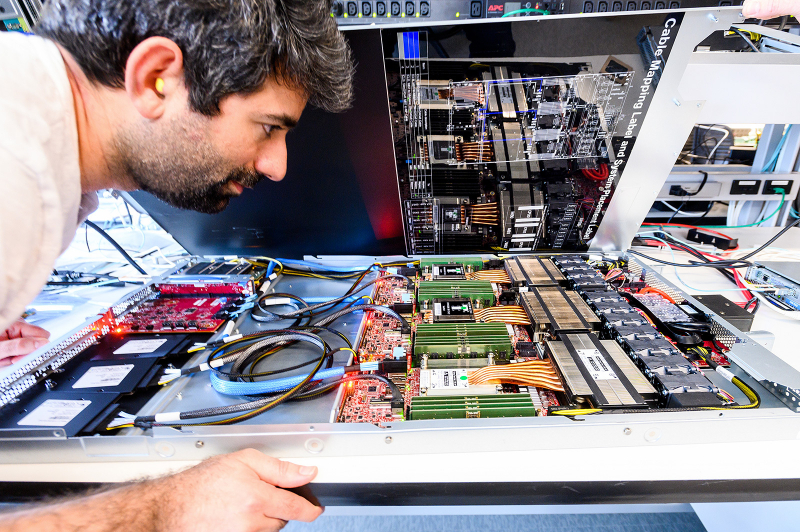

Intel представила процессоры Xeon D-1800/2800 и E-2400 для edge-систем и серверов начального уровняНаряду с анонсом процессоров Xeon Scalable пятого поколения компания Intel обновила и модельные ряды Xeon D и Xeon E. Изменений и нововведений в представленных чипах достаточно много. Так, модельный ряд Xeon D по традиции поделён на две ветви: Xeon D-1800 и Xeon D-2800. Уже сериии Xeon D-1700 и D-2700 были адаптированы для работы в серверах периферийных вычислений и в составе сетевого оборудования. Напомним ключевые моменты:

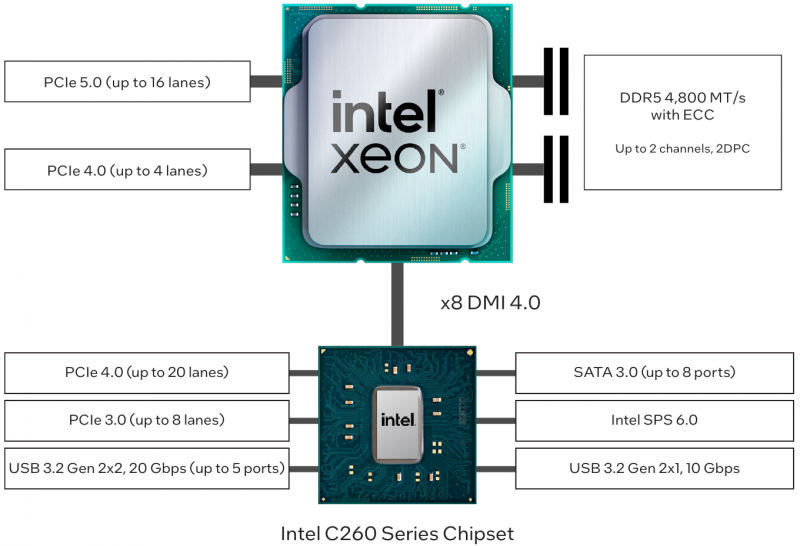

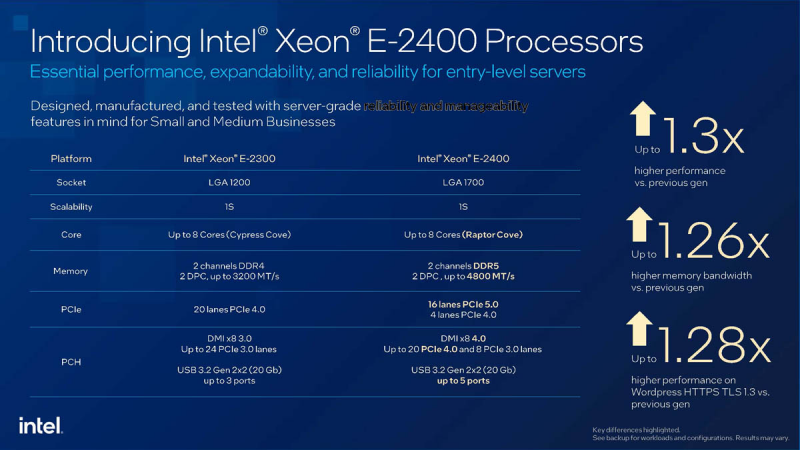

Всё это характерно и для новых Xeon D-1800 и D-2800, ведь в их основе лежит прежняя архитектура Ice Lake-D. Речь всё ещё идёт о сочетании DDR4 и PCI Express 4.0, однако улучшения всё же есть: оптимизация техпроцесса позволила довести максимальное количество ядер до 22 против 20 у предыдущих моделей при неизменном теплопакете. Небольшой прирост производительности тоже есть — примерно 1,12-1,15х у старшей модели Xeon D-2800. Кроме того, процессоры Xeon D-1800, наконец, получили поддержку двух 100GbE-портов. Одновременно с анонсом новых Xeon D состоялся анонс серии Xeon E-2400, которая заменит Xeon E-2300. Изменений здесь существенно больше. Во-первых, платформа перебралась с LGA 1200 на LGA 1700, а на смену ядрам Cypress Cove пришли Raptor Cove. И хотя E-ядер в составе CPU нет, Intel почему-то решила не активировать поддержку AVX-512. Во-вторых, существенный апгрейд претерпела подсистема памяти: вместо двух каналов DDR4-3200 теперь доступна пара каналов DDR5-4800. Наконец, Xeon E-2400 получили поддержку PCI Express 5.0 — из 20 имеющихся процессорных линий 16 теперь способны работать именно в этом режиме. Подросла версия DMI с 3.0 до 4.0, а PCH новой платформы теперь предоставляет 20 линий PCIe 4.0 и 8 линий PCIe 3.0. Заодно с трёх до пяти выросло количество портов USB 3.2 Gen 2x2 (20 Гбит/с). Максимальное число ядер в новой серии Xeon E осталось прежним — их всё ещё восемь, но благодаря существенно более быстрой памяти и использованию техпроцесса Intel 7 Ultra производительность новинок в среднем в 1,3 раза выше, чем у предшественников. Базовая частота подросла до 3,5 ГГц, в турборежим частота доходит до 5,6 ГГц, но при этом теплопакет не выходит за рамки 95 Вт. Нацелены Intel Xeon E-2400 на рынок серверов и облачных систем начального уровня.

30.11.2023 [14:18], Сергей Карасёв

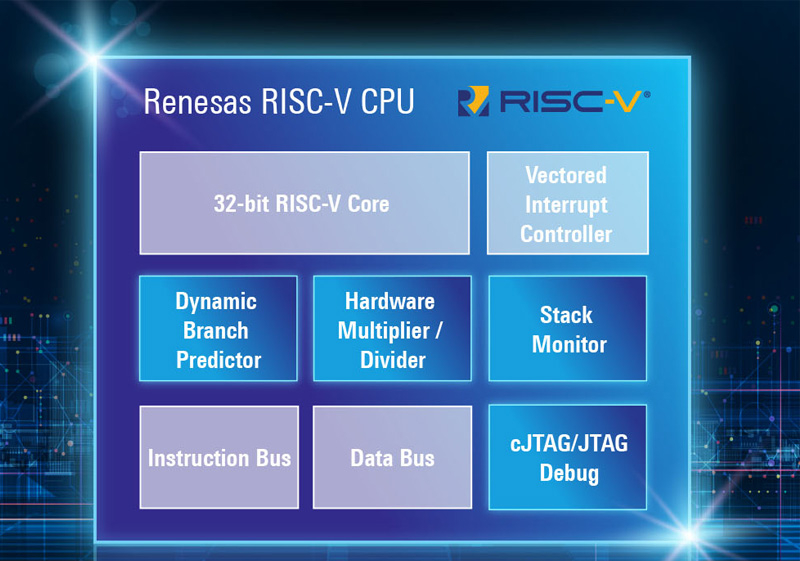

Renesas представила собственное 32-бит ядро RISC-VКомпания Renesas Electronics объявила о создании собственного 32-битного процессорного ядра на основе архитектуры набора команд RISC-V (ISA) с открытым исходным кодом. Решение дополнит существующее семейство 32-бит микроконтроллеров (MCU) Renesas, включая проприетарные изделия RX и RA на архитектуре Arm Cortex-M. RISC-V-ядро Renesas предназначено для создания чипов общего назначения. Предполагается, что такие процессоры найдут применение в устройствах Интернета вещей, потребительской электронике, медицинском оборудовании, индустриальных системах и пр.

Источник изображения: Renesas Новое ядро может выполнять функции основного контроллера приложений или дополнительного вторичного узла в SoC. Кроме того, ядро подходит для применения в составе внутрикристальных подсистем и специализированных изделий (ASSP). Производительность оценивается в 3,27 CoreMark/МГц, что, как утверждает Renesas, превосходит показатель других сопоставимых по классу решений, представленных на рынке. В ядре Renesas реализованы некоторые расширения RISC-V ISA: это M (целочисленное умножение/деление), А (атомарные операции с памятью), С (сжатый формат команд; подмножество RV32I) и В (инструкции для манипуляций с битами). Компания Renesas планирует выпустить свой первый MCU на базе RISC-V и соответствующие инструменты разработки в I квартале 2024 года. Тогда же будут обнародованы технические подробности о продукте.

29.11.2023 [03:43], Владимир Мироненко

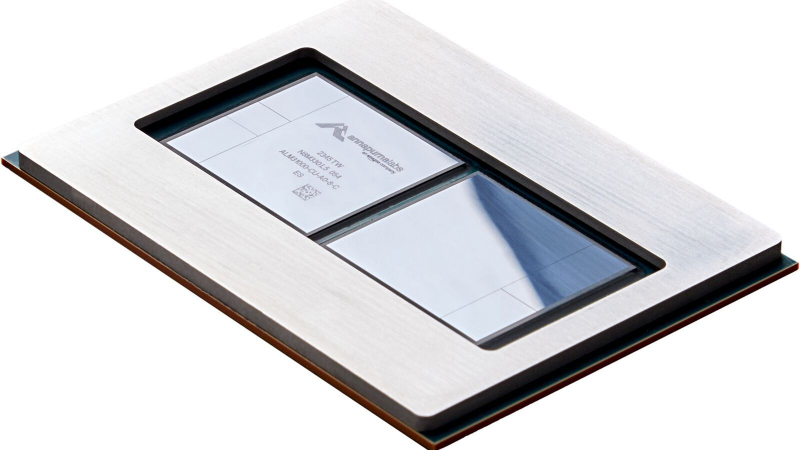

AWS представила 96-ядерный Arm-процессор Graviton4 и ИИ-ускоритель Trainium2Amazon Web Services представила Arm-процессор нового поколения Graviton4 и ИИ-ускоритель Trainium2, предназначенный для обучения нейронных сетей. Всего к текущему моменту компания выпустила уже 2 млн Arm-процессоров Graviton, которыми пользуются более 50 тыс. клиентов. «Graviton4 представляет собой четвёртое поколение процессоров, которое мы выпустили всего за пять лет, и это самый мощный и энергоэффективный чип, который мы когда-либо создавали для широкого спектра рабочих нагрузок», — отметил Дэвид Браун (David Brown), вице-президент по вычислениям и сетям AWS. По сравнению с Graviton3 новый чип производительнее на 30 %, включает на 50 % больше ядер и имеет на 75 % выше пропускную способность памяти. Graviton4 будет иметь до 96 ядер Neoverse V2 Demeter (2 Мбайт L2-кеша на ядро) и 12 каналов DDR5-5600. Кроме того, новый чип получит поддержку шифрования трафика для всех своих аппаратных интерфейсов. Процессор изготавливается по 4-нм техпроцессу TSMC и, вероятно, имеет чиплетную компоновку. Возможно, это первый CPU компании, ориентированный на работу в двухсокетных платформах. Поначалу Graviton4 будет доступен в инстансах R8g (пока в статусе превью), оптимизированных для приложений, интенсивно использующих ресурсы памяти — высокопроизводительные базы данных, in-memory кеши и Big Data. Эти инстансы будут поддерживать более крупные конфигурации, иметь в три раза больше vCPU и в три раза больше памяти по сравнению с инстансами Rg7, которые имели до 64 vCPU и 512 Гбайт ОЗУ. В свою очередь, Trainium 2 предназначен для обучения больших языковых моделей (LLM) и базовых моделей. Сообщается, что ускоритель в сравнении с Trainium 1 вчетверо производительнее и при этом имеет в 3 раза больший объём памяти и в 2 раза более высокую энергоэффективность. Инстансы EC2 Trn2 получат 16 ИИ-ускорителей с возможностью масштабирования до 100 тыс. единиц в составе EC2 UltraCluster, которые суммарно дадут 65 Эфлопс, то есть по 650 Тфлопс на ускоритель. Как утверждает Amazon это позволит обучать LLM с 300 млрд параметров за недели вместо месяцев. Со временем на Graviton4 заработает SAP HANA Cloud, портированием и оптимизацией этой платформы уже занимаются. Oracle также перенесла свою СУБД на Arm, а заодно перевела все свои облачные сервисы на чипы Ampere, в которую в своё время инвестировала. Microsoft же пошла по пути AWS и недавно анонсировала 128-ядерый Arm-процессор (Neoverse N2) Cobalt 100 и ИИ-ускоритель Maia 100 собственной разработки. Всё это может представлять отдалённую угрозу для AMD и Intel. С NVIDIA же все всё равно пока что продолжают дружбу — именно в инфраструктуре AWS, как ожидается, появится самый мощный в мире ИИ-суперкомпьютер на базе новых GH200.

25.11.2023 [19:56], Сергей Карасёв

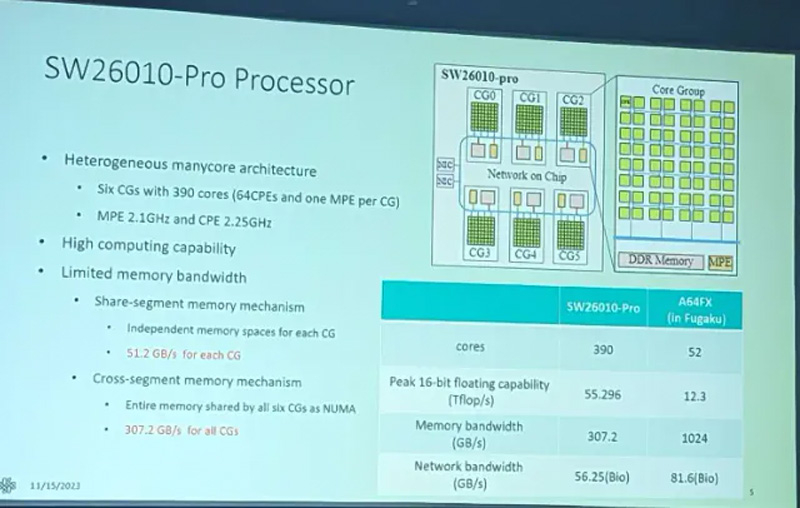

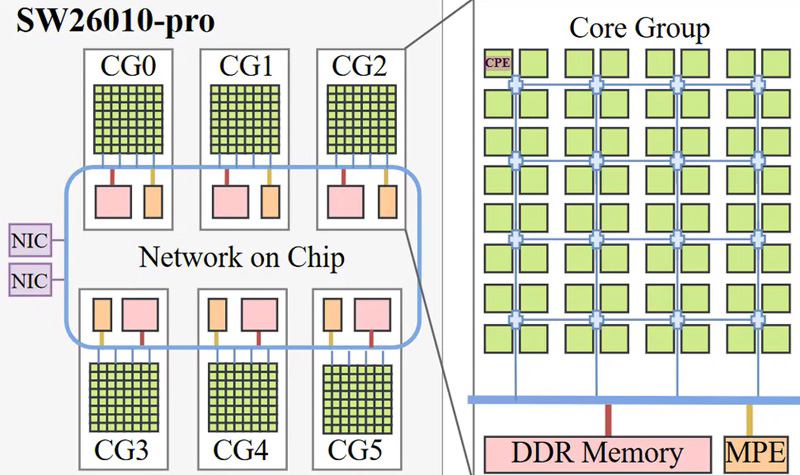

Китайский процессор Sunway SW26010 Pro с 384 ядрами обеспечивает быстродействие 13,8 ТфлопсНа фоне американских санкций Китай ведёт активную разработку собственных процессоров. Одним из таких изделий является чип Sunway SW26010-Pro для суперкомпьютеров и НРС-систем. Недавно, как сообщает ресурс Tom's Hardware, были раскрыты характеристики этого изделия. Процессор SW26010-Pro, первая информация о котором появилась в 2021 году, является значительно улучшенной версией модели SW26010. От прародителя Pro-вариант унаследовал базовую архитектуру.

Источник изображений: Chips and Cheese Решение SW26010-Pro использует 64-битную платформу RISC. В состав чипа входят шесть групп ядер (Core Group, CG) и блок обработки протоколов (Protocol Processing Unit, PPU). Каждый узел CG содержит 64 вычислительных элемента (Compute Processing Element, CPE) с 512-бит векторным механизмом, а также 256 Кбайт быстрого кеша данных и 16 Кбайт кеша для инструкций. Таким образом, общее количество ядер достигает 384 против 256 у обычной версии SW26010. Кроме того, в конструкцию SW26010-Pro входит один элемент обработки управления (Management Processing Element, MPE) в расчёте на узел CG: это суперскалярное ядро с внеочередным исполнением и векторным движком, 32 Кбайт кеша инструкций и 32 Кбайт кеша данных L1, 256 Кбайт кеша L2 и 128-бит интерфейсом памяти DDR4-3200. MPE и CPE используют протокол на основе директорий, который обеспечивает согласованный обмен данными. Это сокращает объём информации, которой обмениваются ядра, и гарантирует точное взаимодействие, что важно для приложений с нерегулярным доступом к совместно используемым данным.  Процессор SW26010-Pro функционирует на частотах 2,25 ГГц для CPE и 2,10 ГГц для MPE против 1,45 ГГц (в обоих случаях) у предшественника. Заявленная производительность достигает 13,8 Тфлопс FP64 и 27,6 Тфлопс FP32. Для сравнения: у обычной модели SW26010 быстродействие FP64 равно 2,9 Тфлопс, а у процессора AMD EPYC 9654 Genoa — 5,4 Тфлопс. Каждый узел CG теперь поддерживает 16 Гбайт памяти DDR4 (против 8 Гбайт DDR3 у SW26010), а максимально допустимый объём ОЗУ достигает 96 Гбайт. При этом, как отмечается, у SW26010 Pro сохраняются ограничения в плане производительности кеша и подсистемы ОЗУ. Так, 256 Кбайт кеша в расчёте на CPE при отсутствии надлежащего кеша L2 недостаточно, а двухканальной подсистемы памяти DDR4-3200 (51,2 Гбайт/с) едва хватает на 64 ядра, каждое из которых имеет 512-бит векторный FPU и обеспечивает производительность до 16 Флопс/цикл (FP64).

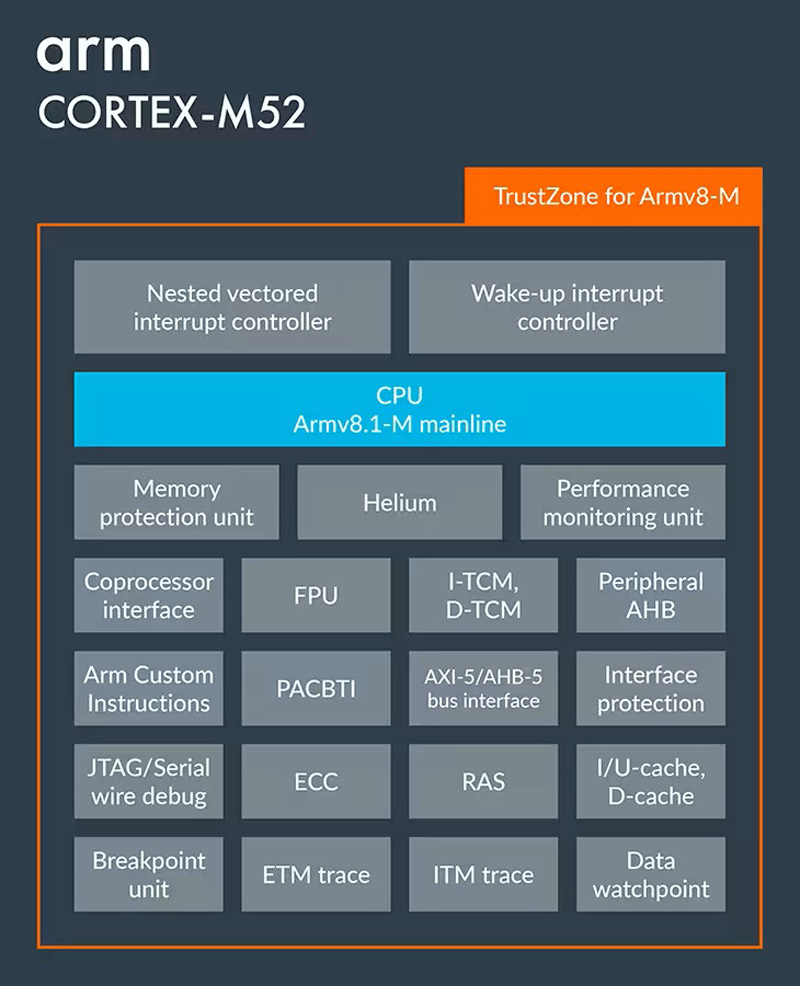

25.11.2023 [10:30], Сергей Карасёв

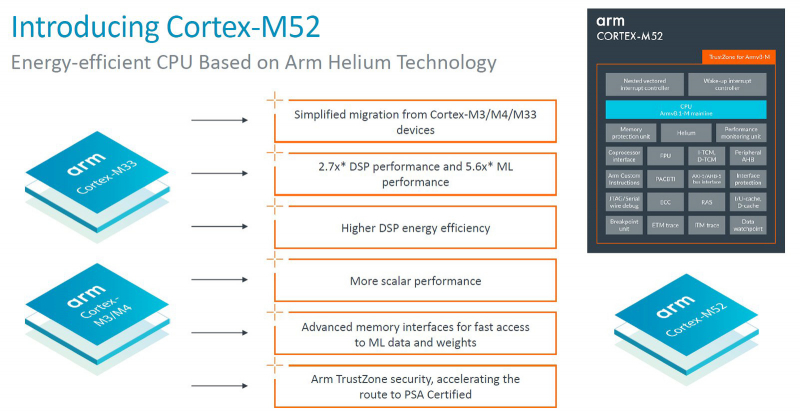

Arm представила Cortex-M52 — компактное ИИ-ядро для Интернета вещейКомпания Arm анонсировала Cortex-M52 — своё самое компактное и энергоэффективное ядро, поддерживающее работу с векторными расширениями Helium. Новинка предназначена для использования в небольших и недорогих устройствах Интернета вещей (IoT), наделённых ИИ-функциями. Изделие выполнено на архитектуре Armv8.1-M. Реализованы 32-битные шины AMBA 5 AXI, AMBA 5 AHB для периферии и AMBA 5 AHB TCM (Tightly Coupled Memory). За безопасность отвечают средства Arm TrustZone. Поддерживаются 32-битные расширения DSP/SIMD. В перечень опций входит FPU-блок с возможностью выполнения операций FP16, FP32 и FP64. Для Cortex-M52 предусмотрено использование по 64 Кбайт кеша инструкций и данных с поддержкой ECC (опционально), а также до 16 Мбайт Instruction TCM (ITCM) и Data TCM (DTCM). По заявлениям Arm, производительность Cortex-M52 на операциях машинного обучения в 5,6 раза превышает показатель у решений предыдущего поколения, таких как Cortex-M33, причём без необходимости использования специального блока (NPU). Эффективность достигает 4,3 CoreMark/МГц и 1,6 DMIPS/МГц.  Среди ключевых вариантов использования Cortex-M52 названы энергоэффективные микроконтроллеры для потребительских устройств с батарейным питанием, носимые гаджеты со средствами машинного обучения и интеллектуальные промышленные датчики. В плане программной части новое ядро полностью совместимо с Cortex-M55 и Cortex-M85. Говорится, что благодаря Cortex-M52 клиенты смогут внедрять интеллектуальные функции в приложения и устройства на периферии при гораздо меньших затратах, чем это возможно в настоящее время.

22.11.2023 [13:23], Сергей Карасёв

Китайцы разработали серверный процессор на архитектуре IBM PowerКитайская компания Hexin Technology, по сообщению ресурса Tom's Hardware, создала тестовый чип второго поколения (Test Chip 2, TC2) в рамках проекта по разработке серверного процессора HX-C2000. Данная инициатива является очередной попыткой КНР разработать альтернативы зарубежным изделиям, поставки которых в страну ограничены из-за жёстких санкций со стороны США. Большинство современных серверных процессоров используют архитектуры x86, Arm или RISC-V. Компания Hexin пошла по другому пути. Она проектирует чипы на архитектуре набора команд (ISA) Power корпорации IBM. Эта архитектура была переведена в разряд открытых решений в 2019 году, а в 2021-м сообщалось, что IBM и Inspur создали совместное предприятие для разработки мощных серверных систем на базе Power.

Источник изображения: Jiwei.com В 2022 году компания Hexin изготовила тестовые чипы HX-C2000 TC1, а теперь произведены изделия TC2. Они насчитывают приблизительно 110 млрд транзисторов. Характеристики процессоров, такие как количество RISC-ядер и поддерживаемые интерфейсы, не раскрываются. Известно, что штат Hexin насчитывает примерно 400 сотрудников, многие из которых ранее работали в исследовательском подразделении IBM. Чипы HX-C2000 планируется применять в серверах, ориентированных на приложения ИИ, обработку больших данных, облачные вычисления и пр. Говорится, что новый процессор практически готов к выпуску, а его массовое производство планируется организовать в 2024 году. При этом, однако, могут возникнуть сложности с доступностью совместимого ПО.

16.11.2023 [02:43], Алексей Степин

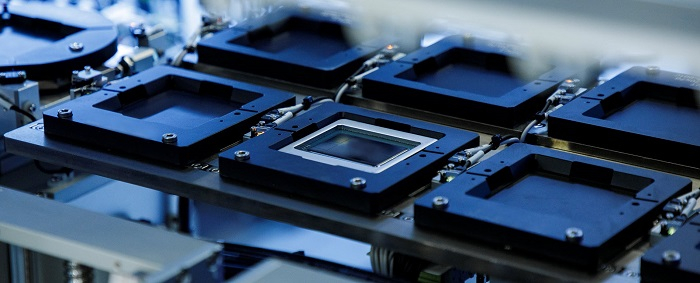

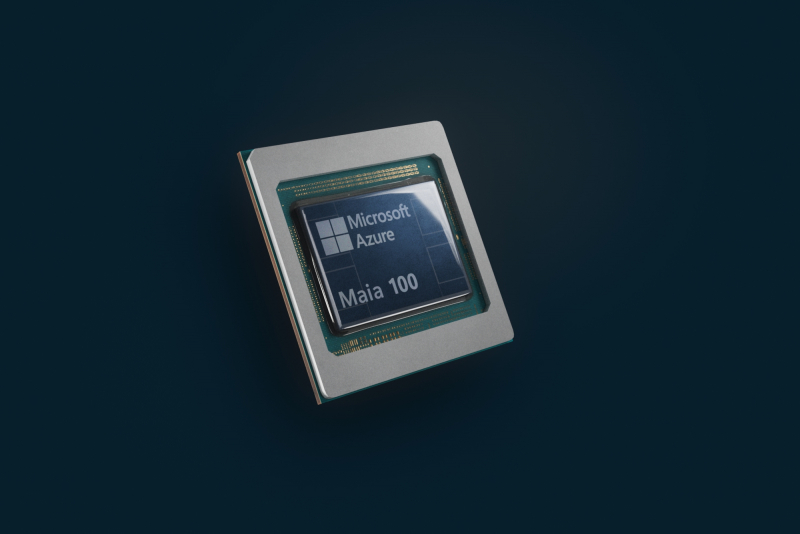

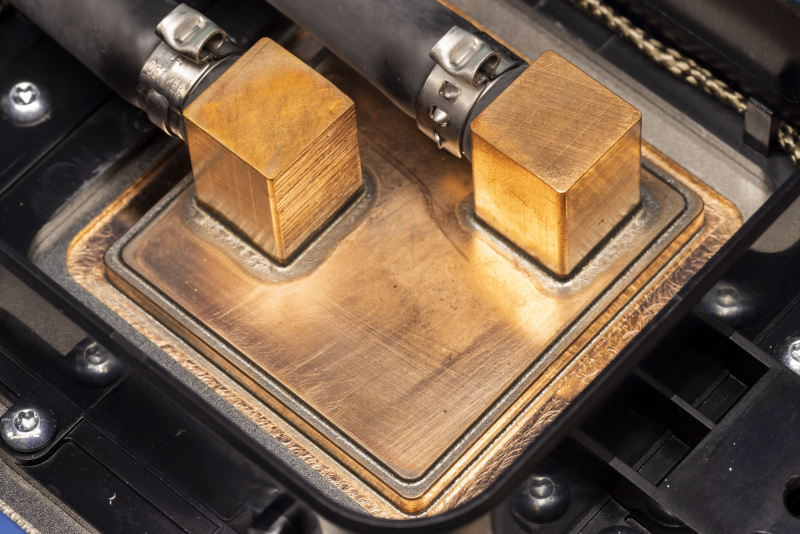

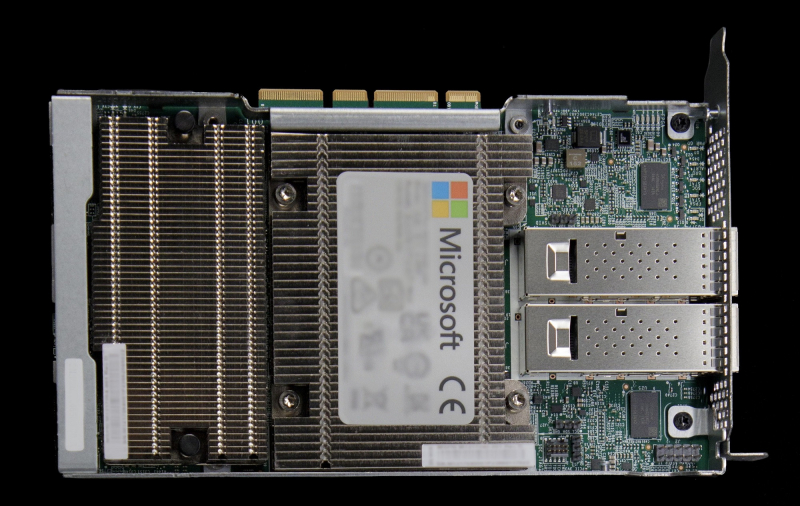

Microsoft представила 128-ядерый Arm-процессор Cobalt 100 и ИИ-ускоритель Maia 100 собственной разработкиГиперскейлеры ради снижения совокупной стоимости владения (TCO) и зависимости от сторонних вендоров готовы вкладываться в разработку уникальных чипов, изначально оптимизированных под их нужды и инфраструктуру. К небольшому кругу компаний, решившихся на такой шаг, присоединилась Microsoft, анонсировавшая Arm-процессор Azure Cobalt 100 и ИИ-ускоритель Azure Maia 100. Первопроходцем в этой области стала AWS, которая разве что память своими силами не разрабатывает. У AWS уже есть три с половиной поколения Arm-процессоров Graviton и сразу два вида ИИ-ускорителей: Trainium для обучения и Inferentia2 для инференса. Крупный китайский провайдер Alibaba Cloud также разработал и внедрил Arm-процессоры Yitian и ускорители Hanguang. Что интересно, в обоих случаях процессоры оказывались во многих аспектах наиболее передовыми. Наконец, у Google есть уже пятое поколение ИИ-ускорителей TPU. Microsoft заявила, что оба новых чипа уже производятся на мощностях TSMC с использованием «последнего техпроцесса» и займут свои места в ЦОД Microsoft в начале следующего года. Как минимум, в случае с Maia 100 речь идёт о 5-нм техпроцессе, вероятно, 4N. В настоящее время Microsoft Azure находится в начальной стадии развёртывания инфраструктуры на базе новых чипов, которая будет использоваться для Microsoft Copilot, Azure OpenAI и других сервисов. Например, Bing до сих пор во много полагается на FPGA, а вся ИИ-инфраструктура Microsoft крайне сложна. Microsoft приводит очень мало технических данных о своих новинках, но известно, что Azure Cobalt 100 имеет 128 ядер Armv9 Neoverse N2 (Perseus) и основан на платформе Arm Neoverse Compute Subsystem (CSS). По словам компании, процессоры Cobalt 100 до +40 % производительнее имеющихся в инфраструктуре Azure Arm-чипов, они используются для обеспечения работы служб Microsoft Teams и Azure SQL. Oracle, вложившаяся в своё время в Ampere Comptuing, уже перевела все свои облачные сервисы на Arm. Чип Maia 100 (Athena) изначально спроектирован под задачи облачного обучения ИИ и инференса в сценариях с использованием моделей OpenAI, Bing, GitHub Copilot и ChatGPT в инфраструктуре Azure. Чип содержит 105 млрд транзисторов, что больше, нежели у NVIDIA H100 (80 млрд) и ставит Maia 100 на один уровень с Ponte Vecchio (~100 млрд). Для Maia организован кастомный интерконнект на базе Ethernet — каждый ускоритель располагает 4,8-Тбит/с каналом для связи с другими ускорителями, что должно обеспечить максимально эффективное масштабирование. Сами Maia 100 используют СЖО с теплообменниками прямого контакта. Поскольку нынешние ЦОД Microsoft проектировались без учёта использования мощных СЖО, стойку пришлось сделать более широкой, дабы разместить рядом с сотней плат с чипами Maia 100 серверами и большой радиатор. Этот дизайн компания создавала вместе с Meta✴, которая испытывает аналогичные проблемы с текущими ЦОД. Такие стойки в настоящее время проходят термические испытания в лаборатории Microsoft в Редмонде, штат Вашингтон. В дополнение к Cobalt и Maia анонсирована широкая доступность услуги Azure Boost на базе DPU MANA, берущего на себя управление всеми функциями виртуализации на манер AWS Nitro, хотя и не целиком — часть ядер хоста всё равно используется для обслуживания гипервизора. DPU предлагает 200GbE-подключение и доступ к удалённому хранилищу на скорости до 12,5 Гбайт/с и до 650 тыс. IOPS. Microsoft не собирается останавливаться на достигнутом: вводя в строй инфраструктуру на базе новых чипов Cobalt и Maia первого поколения, компания уже ведёт активную разработку чипов второго поколения. Впрочем, совсем отказываться от партнёрства с другими вендорами Microsoft не намерена. Компания анонсировала первые инстансы с ускорителями AMD Instinct MI300X, а в следующем году появятся инстансы с NVIDIA H200.

14.11.2023 [16:36], Сергей Карасёв

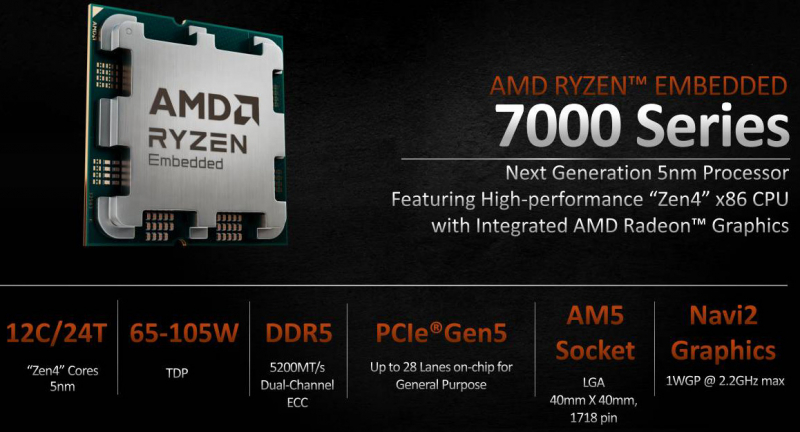

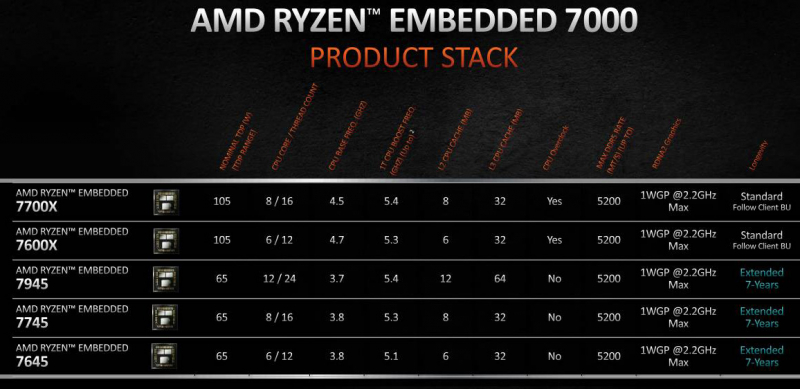

AMD представила встраиваемые процессоры Ryzen Embedded 7000 с графикой RDNA2Компания AMD анонсировала процессоры Ryzen Embedded 7000 на архитектуре Zen 4, предназначенные для использования во встраиваемых системах. О намерении представить продукты на этих чипах сообщили многие известные производители, включая Advantech, ASRock и DFI. Ryzen Embedded 7000 — это первые «встраиваемые» процессоры AMD, при изготовлении которых применяется 5-нм технология. AMD гарантирует, что чипы данной серии будут доступны в течение семи лет. Говорится о совместимости с Windows Server, Windows 10/11, а также Ubuntu Linux. Процессоры получили исполнение AM5. В серию вошли пять моделей (см. таблицу ниже), количество вычислительных ядер у которых в зависимости от модификации равно 6, 8 или 12. Есть SMT. Базовая тактовая частота варьируется от 3,7 до 4,5 ГГц, частота в турбо-режиме — от 5,1 до 5,4 ГГц. Объём кеша L2 равен 1 Мбайт на ядро. Размер кеша L3 составляет 32 или 64 Мбайт. Показатель TDP равен 65 Вт у младших версий и 105 Вт у старших. Чипы семейства Ryzen Embedded 7000 получили контроллер оперативной памяти DDR5-5200 ECC и интегрированную графику RDNA2. Обеспечивается поддержка 28 линий PCIe 5.0. Изделия рассчитаны на системы автоматизации, машинного зрения и другие индустриальные применения.

13.11.2023 [13:56], Сергей Карасёв

Synopsys представила ядра ARC-V на архитектуре RISC-VКомпания Synopsys анонсировала процессорные ядра ARC-V на архитектуре RISC-V, которые будут доступны для лицензирования сторонним разработчикам. Заказчики смогут воспользоваться сопутствующими инструментами, включая средства автоматизации проектирования электронных устройств на базе ИИ Synopsys.ai. В семейство Synopsys ARC-V Processor IP вошли модификации с высоким и средним уровнями производительности, а также версия со сверхнизким энергопотреблением. Разработчики смогут воспользоваться платформой Synopsys MetaWare для создания эффективного и высокооптимизированного кода.

Источник изображения: Synopsys Кроме того, анонсировано ядро Synopsys ARC-V Functional Safety (FS) со встроенными аппаратными функциями безопасности для обнаружения системных ошибок. Говорится об уровнях безопасности ASIL B и ASIL D. Изделие разработано на основе системы управления качеством (QMS) Synopsys, сертифицированной по стандарту ISO 9001. А пакет MetaWare Development Toolkit for Safety поможет разработчикам ускорить написание кода, соответствующего стандарту ISO 26262. 32-битное ядро Synopsys ARC-V RMX для встраиваемых систем станет доступно во II квартале 2024 года. 32-битное ядро реального времени Synopsys ARC-V RHX и 64-битное ядро Synopsys ARC-V RPX IP планируется выпустить во второй половине следующего года. Synopsys также сообщила, что её представитель войдёт в состав совета директоров и технический руководящий комитет некоммерческой организации RISC-V International, которая занимается координацией разработки данной архитектуры.

09.11.2023 [03:15], Алексей Степин

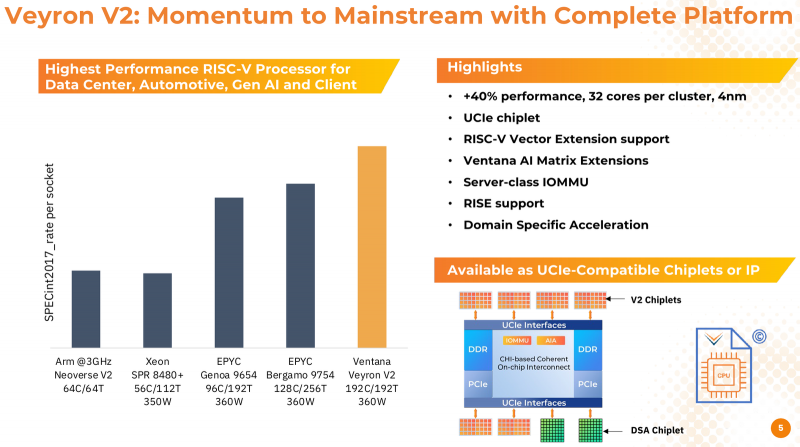

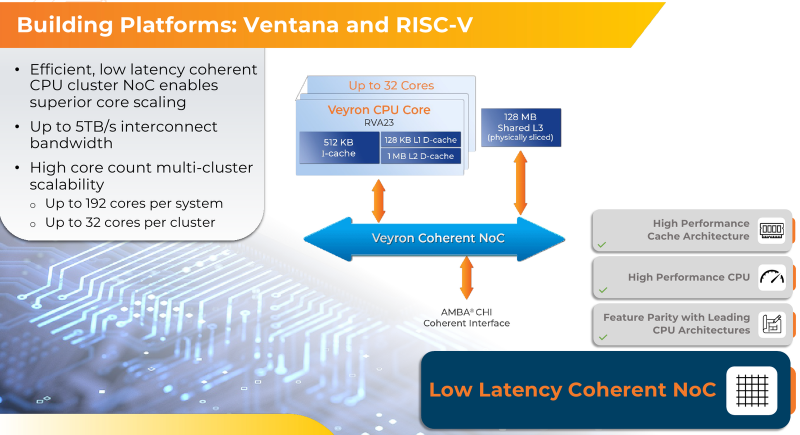

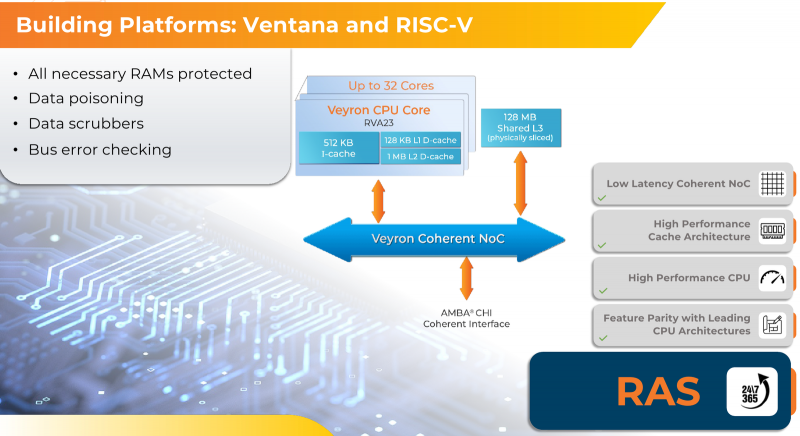

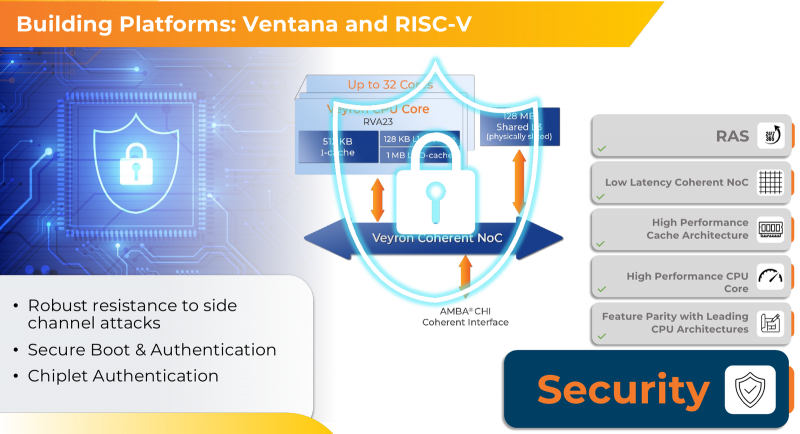

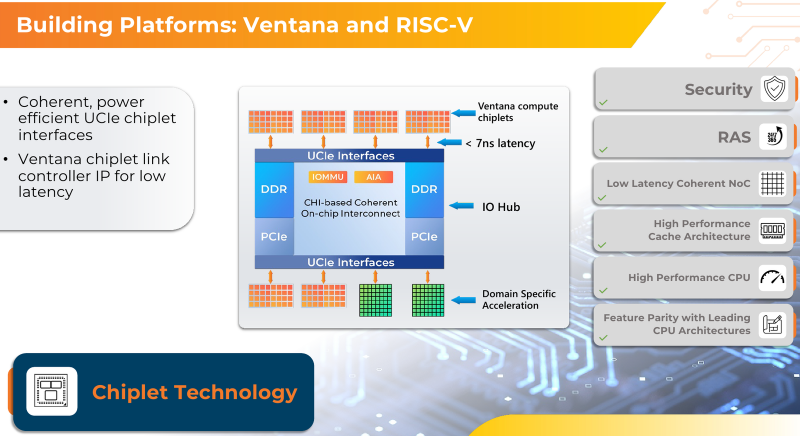

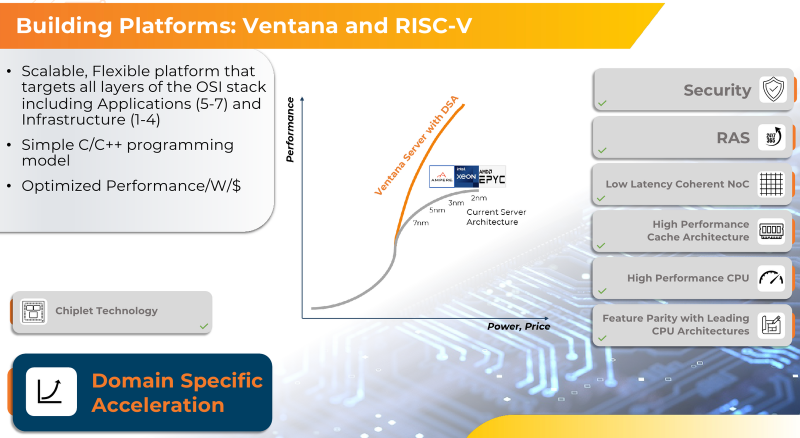

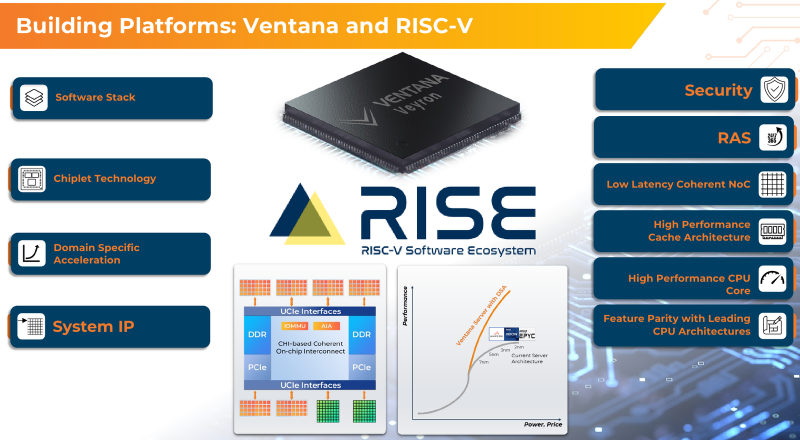

RISC-V с приправой: модульные 192-ядерные серверные процессоры Ventana Veyron V2 можно дополнить ускорителямиВ 2022 года компания Ventana Micro Systems анонсировала первые по-настоящему серверные RISC-V процессоры Veyron V1. Анонс чипов, обещающих потягаться на равных с лучшими x86-процессорами с архитектурой x86, прозвучал громко. Популярности, впрочем, Veyron V1 не снискал, но на днях компания анонсировала второе поколение чипов Veyron V2, более полно воплотившее в себе принципы модульного дизайна и получившее ряд усовершенствований. Как и в первом поколении, компания-разработчик продолжает придерживаться концепции «процессора-конструктора» с чиплетным дизайном. В центре 4-нм Veyron V2 по-прежнему лежит I/O-хаб на базе AMBA CHI, охватывающий контроллеры памяти и шины PCI Express, а также блоки IOMMU и AIA. К нему посредством интерфейса UCIe подключаются вычислительные чиплеты. Латентность UCIe-подключения составляет менее 7 нс.

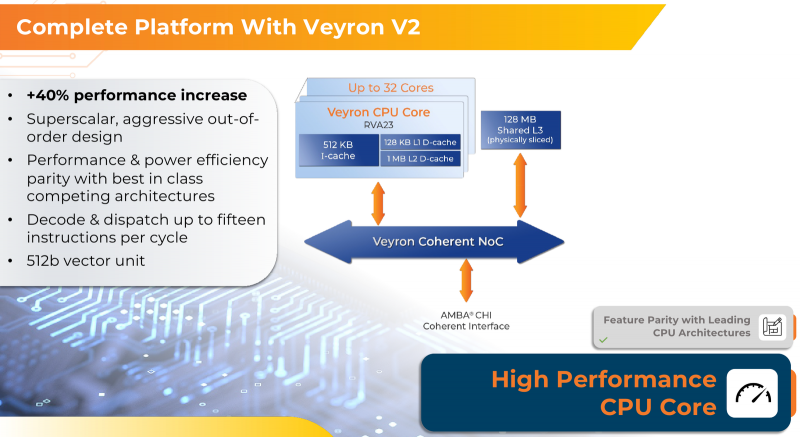

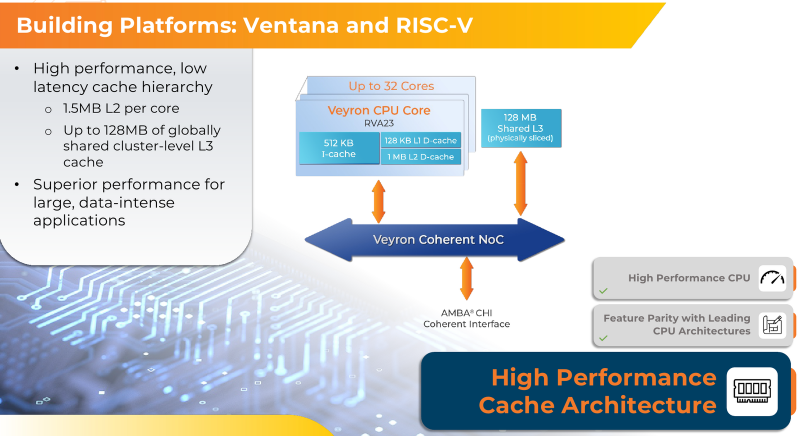

Источник изображений здесь и далее: Ventana Micro Systems Чиплеты эти могут быть разных видов: либо с ядрами общего назначения (по 32 ядра на чиплет), образующие собственно процессор Veyron V2, либо содержащие специфические сопроцессоры под конкретную задачу (domain-specific acceleration, DSA). Последние могуть быть представлены FPGA, ИИ-ускорителями и т.д. Более того, Ventana по желанию заказчика может оптимизировать и I/O-хаб для повышения эффективности работы ядер CPU с сопроцессорами. В классическом варианте Veyron V2 может иметь до шести чиплетов с RV64GC-ядрами V2, что в сумме даёт 192 ядра. Поддержка SMT отсутствует. Удельная производительность в пересчёте на ядро получается несколько ниже, чем у AMD Zen 4c, но согласно результатам тестов, предоставленных Ventana, 192-ядерный Veyron V2 заметно опережает AMD EPYC Bergamo 9754 (128C/256T) при аналогичном теплопакете в 360 Вт. Столь неплохой результат достигнут за счёт оптимизации архитектуры Veyron: по сравнению с первым поколением говорится о 40 % прибавке производительности. Что немаловажно, во втором поколении процессоров Veyron была реализована поддержка 512-бит векторных расширений, фирменных матричных расширений, а также целого ряда других спецификаций. В целом ради совместимости разработчики предпочли остаться в рамках общего профиля RVA23. Сами ядра V2 используют суперскалярный дизайн с агрессивным внеочередным исполнением и продвинутым предсказанием ветвлений. Возможно декодирование и обработка до 15 инструкций за такт. Объём L1-кешей составляет 512 Кбайт для инструкций и 128 Кбайт для данных, дополнительно каждое ядро имеет свой кеш L2 объёмом 1 Мбайт. Общий для всего 32-ядерного чиплета L3-кеш имеет объём 128 Мбайт. Производительность внутренней когерентной шины составляет до 5 Тбайт/с. Позиционируемый в качестве решения для гиперскейлеров, крупных ЦОД и HPC, Veyron V2 имеет развитые средства предотвращения ошибок и защиты данных, от ECC-кешей и поддержки Secure Boot до аутентификации на уровне чиплета и продвинутых RAS-функций. Кроме того, реализована защита от атак по сторонним каналам. Несмотря на то, что мир RISC-V пока ещё похож на «Дикий Запад», Ventana старается опираться на развитые и популярные стандарты: в частности, это выражается в применении UCIe для подключения чиплетов, поддержку гипервизоров первого и второго типа, вложенную виртуализацию и совместимость с программной экосистемой RISC-V RISE. Подход Ventana позволит избежать недостатков, свойственных дискретным PCIe-ускорителям (высокая латентность, энергопотребление и стоимость) и сложным монолитным SoC (очень высокая стоимость разработки и сроки), снизить время и стоимость стоимость новых решений, а также обеспечить более низкий уровень энергопотребления. В общем, компания явно целится в гиперскейлеров. Видение сценариев применения DSA у Ventana очень широкий — от БД-ускорителей и блоков компрессии-декомпрессии данных до поддержки специфических алгоритмов в задачах аналитики и транскодеров в системах доставки контента. Также становятся ненужными дискретные DPU. Первым партнёром Ventana стала Imagination Technologies, крупный разработчик GPU. В качестве вариантов физической реализации новой платформы Ventana предлагает компактный 1U-сервер, содержащий один чип Veyron V2 со 192 ядрами, работающими на частотах до 3,6 ГГц, и 12 каналами DDR5-5600. Вероятнее всего, производителем новой платформы станет GIGABYTE. Ожидать первых поставок следует не ранее II квартала 2024 года. В целом, видение высокопроизводительной модульной платформы, продвигаемое Ventana, выглядит перспективно, а упор на применение DSA может выгодно отличать её большинства Arm-серверов, конкурирующих с решениями Intel/AMD лоб в лоб. Вопрос лишь в поддержке со стороны разработчиков программного обеспечения — и здесь может сыграть ставка разработчиков на максимально открытые, широкие стандарты. |

|