Материалы по тегу: synopsys

|

15.01.2025 [11:24], Владимир Мироненко

В совет директоров UALink вошли представители Alibaba, Apple и SynopsysКонсорциум Ultra Accelerator Link (UALink) объявил о расширении состава совета директоров представителями Alibaba Cloud, Apple и Synopsys. Новые члены совета будут использовать свои отраслевые знания для продвижения разработки и внедрения в отрасли UALink — высокоскоростного масштабируемого интерконнекта для производительных ИИ-кластеров следующего поколения, указано в пресс-релизе. Фактически UALink занят созданием более открытой альтернативы NVLink. С момента основания в конце октября 2024 года количество участников UALink выросло до более чем 65 компаний, сообщил Куртис Боуман (Kurtis Bowman), председатель совета директоров UALink. Новые участники совета директоров заявили, что совместная работа над интерконнектом для ускорителей будет способствовать повышению эффективности выполнения рабочих нагрузок ИИ. Представитель Apple отметил, что UALink демонстрирует большие перспективы в решении проблем подключения и создании новых возможностей ИИ-индустрии. В консорциум входит широкий круг компаний, от поставщиков облачных услуг и OEM-производителей до разработчиков ПО и полупроводниковых компонентов во главе с AMD, AWS, Astera Labs, Cisco, Google, HPE, Intel, Meta✴ и Microsoft, представляющих основные области разработки решений для повышения производительности нагрузок ИИ.

Источник изображения: UALink Ожидается, что выпуск спецификации UALink 1.0 состоится в I квартале 2025 года. Она предусматривает пропускную способность до 200 Гбит/с на линию и возможность объединения до 1024 ИИ-ускорителей в пределах одного домена.

25.12.2024 [14:45], Руслан Авдеев

Synopsys: в 2025 году ИИ будет напрямую сотрудничать с ИИ над разработкой чиповНа днях глава по стратегии развития ИИ-технологий компании Synopsys Стелиос Диамантидис (Stelios Diamantidis) заявил, что в 2025 году наступит следующая фаза внедрения ИИ. По его словам, ИИ-агенты начнут сотрудничать со своими собратьями с минимальным вмешательством человека, сообщает EE Times. Если ранее ИИ-боты представляли собой рудиментарные системы с заранее заданными правилами и деревьями решений, то теперь они эволюционировали в сложные агентные системы, способные понимать человеческую речь в произвольной форме, генерировать контент, постоянно учиться и менять своё поведение в результате обучения. Такие ИИ-агенты могут быть использованы в специальных случаях и применяться только для определённых приложений, но скоро ситуация может измениться, когда один ИИ-агент сможет взаимодействовать с другим. В блоге Диамантидис добавил, что ИИ-агенты обучаются для улучшения интеграции и взаимодействия, включая разработку чипов.

Источник изображения: Daniel Lonn/unsplash.com В Synopsys сообщили о внутреннем прикладном использовании подобных разработок. По результатам пилотного тестирования внутри компании, генеративный ИИ, как ожидается, сэкономит не менее 250 тыс. часов рабочего времени — сотрудники смогут более продуктивно потратить высвободившееся время на работу с клиентами. Диамантидис добавил, что высокоспециализированные ИИ-агенты могли бы комбинировать и анализировать бессчётные объёмы информации, касающейся разработки полупроводников. Эти задачи могут быть связаны с созданием архитектуры чипа, оптимизацией энергопотребления и др. Сотрудничество ИИ с ИИ может выявлять скрытые закономерности, обеспечивать точные рекомендации по оптимизации проектирования чипов и повышению их производительности.

11.03.2024 [16:47], Алексей Степин

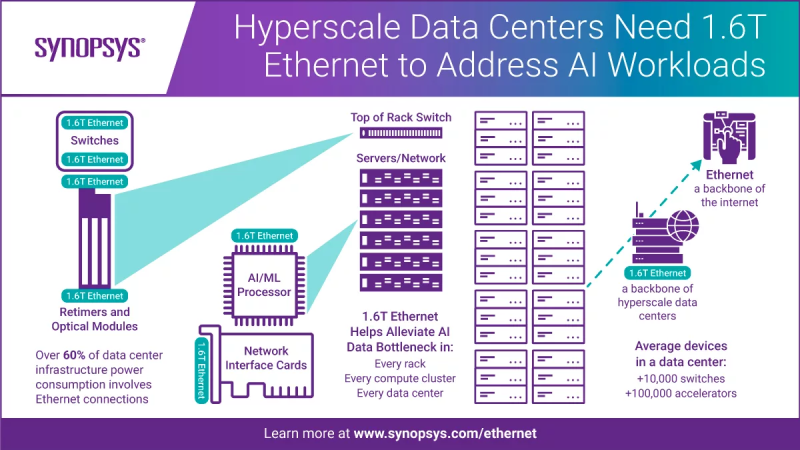

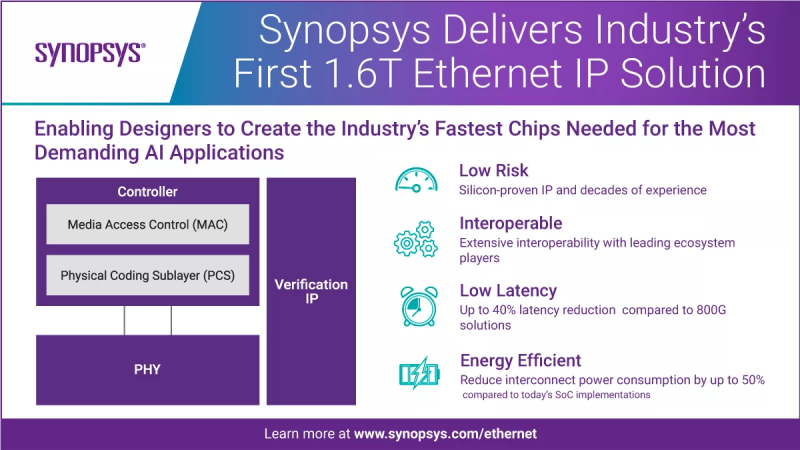

Synopsys завершила разработку платформы Ethernet 1,6 Тбит/сИзвестный разработчик микроэлектроники, компания Synopsys сообщила о завершении работ над новым сверхскоростным вариантом Ethernet, способным работать на скорости 1,6 Тбит/с, что вдвое превышает достигнутые коммерческими решениями на сегодня скорости. Эта разработка нацелена главным образом на рынок крупных ЦОД, особенно связанных с ИИ-технологиями, предъявляющими высокие требования к характеристикам сетевых каналов и интерконнектов. В настоящее время стандарт 1.6TbE не ратифицирован IEEE, и случится это не ранее 2026 года, но Synopsys считает, что применение её наработок в этой области позволит производителям микрочипов начать работу над созданием соответствующих контроллеров уже сейчас. Предварительная версия стандарта 802.3dj, описывающего базовые характеристики таких устройств, должна быть завершена уже в этом году. Дизайн IP-блоков, созданный Synopsys, базируется именно на 802.3dj. Он предусматривает скорости 4 × 400 Гбит/с, 2 × 800 Гбит/с, либо один канал со скоростью 1,6 Тбит/с. В разработке используются блоки SerDes со скоростью 112 и 224 Гбит/с, отвечающие спецификациям OIF-112G и OIF-224G соответственно. В IP-решении Synopsys используются трансмиттеры PAM4, в которых реализована продвинутая обработка сигнала (feed-forward equalization), ресиверы же содержат продвинутый DSP. Это сочетание позволяет соединению работать при потере сигнала в канале, составляющей 45 дБ. Synopsys утверждает, что её технологии позволят реализовать Ethernet со скоростью 1,6 Тбит/с с 50 % экономией площади кремния. Продвинутая архитектура коррекции ошибок при этом должна обеспечить латентность на 40 % ниже в сравнении с классической реализацией. В состав решения Synopsys входят блоки MAC, PCS, контроллер физического уровня (PHY) на основе прошедших тестирование и доказавших свою эффективность SerDes-блоков 224G, а также IP-модуль верификации, который должен помочь разработчикам чипов ускорить и упростить разработку новых сверхскоростных Ethernet-чипов. Все IP-компоненты доступны сейчас и ими уже воспользовались многочисленные клиенты, сообщает Synopsys. Новая разработка Synopsys получила одобрение со стороны консорциума Ethernet.

30.11.2023 [14:15], Сергей Карасёв

Выручка Synopsys бьёт рекорды, а чистая прибыль быстро растётКомпания Synopsys обнародовала показатели работы в IV квартале и 2023 финансовом году в целом, который был завершён 31 октября. Американский разработчик САПР для электроники зафиксировал рекордную выручку и показал значительный рост чистой прибыли. За трёхмесячный период Synopsys получила $1,6 млрд выручки, что является историческим максимумом. Это на 25 % больше результата за последнюю четверть 2022 финансового года, когда показатель равнялся приблизительно $1,3 млрд. Компания подчёркивает, что благодаря активным исследованиям и разработкам смогла улучшить показатели деятельности даже в условиях кризиса и макроэкономических неопределённостей. Чистая квартальная прибыль в годовом исчислении поднялась более чем в два раза — со $153,5 млн до $349,2 млн. Прибыль в пересчёте на одну ценную бумагу составила $2,26 против $0,99 годом ранее. Выручка по итогам 2023 финансового года в целом также оказалась рекордной — примерно $5,8 млрд. Для сравнения: годом ранее Synopsys получила около $5,1 млрд. Таким образом, рост оказался на уровне 15 %. Чистая годовая прибыль достигла $1,2 млрд, или $7,92 на акцию, по сравнению с $984,6 млн, или $6,29 на одну ценную бумагу, в 2022 финансовом году. В I четверти 2024 финансового года, которая продлится до 31 января, Synopsys рассчитывает получить выручку от $1,63 млрд до $1,66 млрд и показать при этом прибыль в диапазоне от $2,4 до $2,5 на акцию. В наступившем финансовом году в целом выручка, как ожидается, составит от $6,57 млрд до $6,63 млрд, чистая прибыль — от $9,07 до $9,25 на одну ценную бумагу.

13.11.2023 [13:56], Сергей Карасёв

Synopsys представила ядра ARC-V на архитектуре RISC-VКомпания Synopsys анонсировала процессорные ядра ARC-V на архитектуре RISC-V, которые будут доступны для лицензирования сторонним разработчикам. Заказчики смогут воспользоваться сопутствующими инструментами, включая средства автоматизации проектирования электронных устройств на базе ИИ Synopsys.ai. В семейство Synopsys ARC-V Processor IP вошли модификации с высоким и средним уровнями производительности, а также версия со сверхнизким энергопотреблением. Разработчики смогут воспользоваться платформой Synopsys MetaWare для создания эффективного и высокооптимизированного кода.

Источник изображения: Synopsys Кроме того, анонсировано ядро Synopsys ARC-V Functional Safety (FS) со встроенными аппаратными функциями безопасности для обнаружения системных ошибок. Говорится об уровнях безопасности ASIL B и ASIL D. Изделие разработано на основе системы управления качеством (QMS) Synopsys, сертифицированной по стандарту ISO 9001. А пакет MetaWare Development Toolkit for Safety поможет разработчикам ускорить написание кода, соответствующего стандарту ISO 26262. 32-битное ядро Synopsys ARC-V RMX для встраиваемых систем станет доступно во II квартале 2024 года. 32-битное ядро реального времени Synopsys ARC-V RHX и 64-битное ядро Synopsys ARC-V RPX IP планируется выпустить во второй половине следующего года. Synopsys также сообщила, что её представитель войдёт в состав совета директоров и технический руководящий комитет некоммерческой организации RISC-V International, которая занимается координацией разработки данной архитектуры. |

|