Материалы по тегу: разработка

|

13.11.2023 [10:10], SN Team

4–5 декабря 2023 года пройдёт открытая конференция ИСП РАН, посвящённая 75-летию отечественных информационных технологий4–5 декабря 2023 года в главном здании Российской академии наук в Москве состоится ежегодная Открытая конференция ИСП РАН им. В.П. Иванникова, посвящённая 75-летию отечественных информационных технологий. Главная цель — обмен результатами фундаментальных исследований и практическим опытом их внедрения. В 2022 году в конференции приняли участие более 650 человек. Организаторами мероприятия выступают Институт системного программирования имени В.П. Иванникова РАН, Российская академия наук, НИЦ «Курчатовский институт», Академия криптографии РФ, Фонд перспективных исследований, международная ассоциация IEEE и IEEE Computer Society. Конференция проводится при поддержке ФСТЭК России. К участию в пленарном заседании приглашены представители руководства РАН, вузов, ИТ-компаний, государственных министерств и ведомств. «Развитие нашего института всегда опиралось на историю. От наших предшественников мы унаследовали великую научную школу и модель работы, основанную на интеграции науки, образования и индустрии. Со временем мы перешли от разработки отдельных технологий к формированию международных сообществ, — рассказал директор ИСП РАН, академик РАН Арутюн Аветисян. — Вместе с десятками компаний и вузов мы создаём репозиторий доверенного системного ПО, работаем над биомедицинскими решениями, повышаем безопасность искусственного интеллекта. Наши технологии внедрены более чем в 100 компаниях, в том числе в Samsung и в «Лаборатории Касперского». Только за последний год более 300 наших патчей добавлены в такие проекты, как ядро Linux, PyTorch и TensorFlow. Вместе с партнёрами мы работаем над обеспечением технологической независимости страны, опираясь на лучшие достижения прошлого, и сохраняем открытость на международном уровне — для успешного будущего». На конференции будут представлены доклады по таким темам, как технологии анализа, моделирования и трансформации программ; управление данными и информационные системы; решение задач механики сплошных сред с использованием СПО; САПР микроэлектронной аппаратуры и лингвистические системы анализа. Состоится также выставка технологий ИСП РАН и компаний-партнёров. Важной частью конференции станет секция «Образование, технологии, сообщество: системный подход к безопасной разработке». Она объединит три тематических блока, которые будут посвящены формированию единой концепции обучения системному программированию, результатам совместной работы ИСП РАН и компаний-партнёров в Технологическом центре исследования безопасности ядра Linux и другим актуальным темам в области кибербезопасности. В секции примут участие представители таких компаний, как «Лаборатория Касперского», «ИнфоТекс», CodeScoring, ГК «Солар», а также представители московских и региональных вузов (МГТУ им. Н.Э. Баумана, Новгородский государственный университет, Чувашский государственный университет и другие). Состоится также традиционный круглый стол «Цифровая медицина», который объединит десятки врачей и ИТ-специалистов и подведёт научно-практические итоги года в этой области. На выставке будут представлены платформа для анализа биомедицинских данных, разработанная в ИСП РАН, и прикладное решение на её основе — сервис для нейросетевой классификации ЭКГ. Посетители смогут прямо на стенде снять ЭКГ, получить консультацию врача и проверить результаты с помощью сервиса нейросетевой классификации. В рамках конференции запланирован II воркшоп «Системы доверенного искусственного интеллекта», в котором примут участие представители Исследовательского центра доверенного искусственного интеллекта (ИЦДИИ) ИСП РАН, а также его индустриальных партнёров («Лаборатория Касперского», «ЕС-Лизинг», «Технопром», «Интерпроком»). Приглашаются также сотрудники других исследовательских центров. Участие в конференции бесплатное, необходимо зарегистрироваться: https://www.isprasopen.ru/#Registration. Сайт мероприятия: https://www.isprasopen.ru/.

23.10.2023 [16:14], Руслан Авдеев

SK Telecom и Deutsche Telekom разработают большие языковые модели специально для телеком-отраслиКомпании SK Telecom (SKT) и Deutsche Telekom объявили о подписании соглашения о намерениях совместной разработки больших языковых моделей (LLM), специально предназначенных для телекоммуникационного бизнеса. Как сообщает блог IEEE Communication Society, готовые решения позволят легко и быстро создавать LLM под свои нужды и другим телеком-компаниям. Первую версию LLM планируют представить в I квартале 2024 года. Это первый плод дискуссий, проходивших в июле 2023 года в рамках группы Global Telco AI Alliance, организованной SKT, Deutsche Telekom, E& и Singtel. SKT и Deutsche Telekom намерены взаимодействовать с компаниями, лидирующими в разработках ИИ-систем, включая Anthropic с её Claude 2 и Meta✴ с её Llama2 — новая базовая LLM будет поддерживать разные языки, включая английский, немецкий, корейский и др.

Источник изображения: Peggy_Marco/pixabay.com Новая языковая модель будет лучше ориентироваться в телеком-специфике, чем LLM общего назначения, поэтому её можно будет использовать, например, в контакт-центрах для помощи живым операторам. В первую очередь это коснётся операторов в Европе, Азии и на Ближнем Востоке — они смогут создавать ИИ-ассистентов с учётом местной специфики. Кроме того, ИИ можно будет применять для мониторинга сетей и выполнения других задач с сопутствующим снижением издержек и ростом эффективности бизнеса в средне- и долгосрочной перспективе. В результате занятые в телеком-бизнесе компании смогут сберечь время и деньги, избежав разработки подобных платформ исключительно собственными силами. Сотрудничество южнокорейской и немецкой компаний будет способствовать расширению глобальной ИИ-экосистемы. Как подчеркнули в Deutsche Telecom, для того, чтобы по максимуму использовать ИИ в сфере поддержки клиентов, LLM будет тренироваться с использованием уникальных данных. В SKT рассчитывают, что сотрудничество двух компаний позволит им завоевать лидирующие позиции в сфере специализированных ИИ-решений, а объединение усилий, ИИ-технологий и инфраструктуры обеспечит новые возможности многочисленным компаниям в разных отраслях. Ранее SK Telecom вложила $100 млн в стартап Anthropic, чтобы получить кастомную LLM для своих нужд.

21.10.2023 [01:01], Алексей Степин

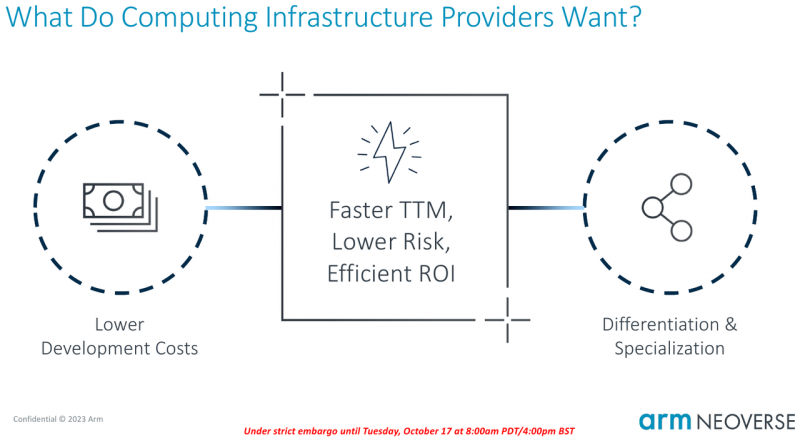

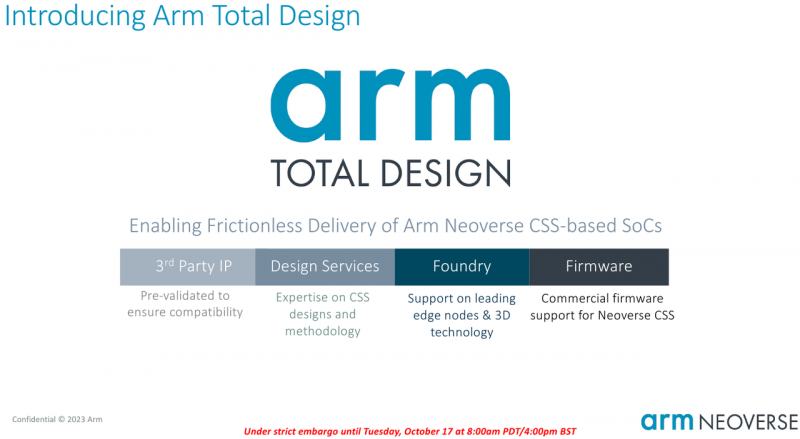

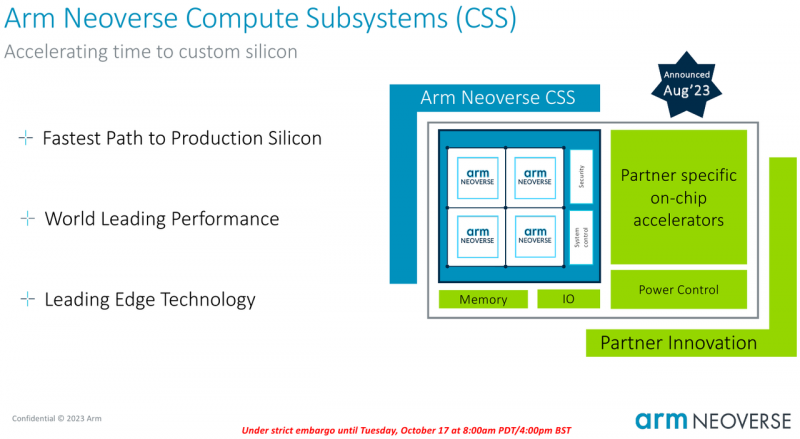

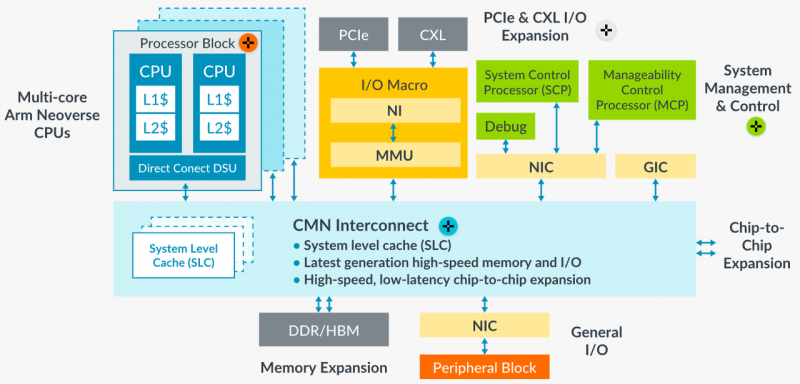

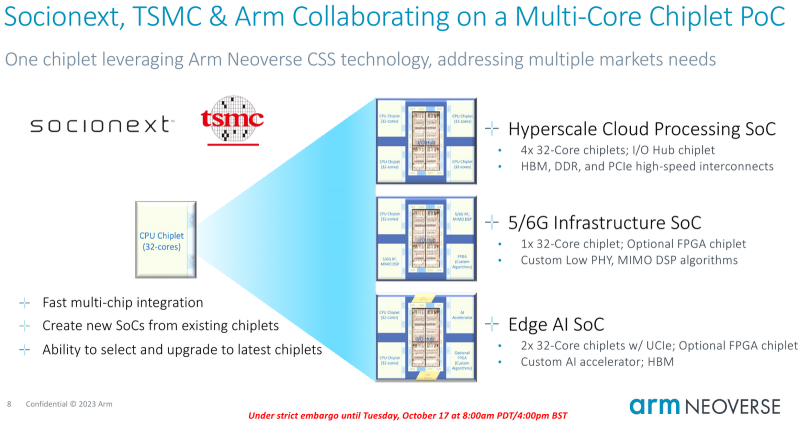

Собери сам: Arm открывает эру кастомных серверных процессоров инициативой Total DesignСегодня на наших глазах в мире процессоростроения происходит серьёзная смена парадигм: от унифицированных архитектур общего назначения и монолитных решений разработчики уходят в сторону модульности и активного использования специфических аппаратных ускорителей. Разумеется Arm не осталась в стороне — на мероприятии 2023 OCP Global Summit компания рассказала о новой инициативе Arm Total Design. Эта инициатива должна помочь как создателям новых процессоров за счёт ускорения процесса разработки и снижения его стоимости, так и владельцам крупных вычислительных инфраструктур. Последние всё больше склоняются к специализации и дифференциации в процессорных архитектурах новых поколений, но ожидают также энергоэффективности, дружественности к экологии и как можно более низкой совокупной стоимости владения. В основе инициативы Arm лежит анонсированная ещё в августе на HotChips 2023 процессорная платформа Arm Neoverse Compute Subsystem (CSS). Neoverse CSS N2 (Genesis) представляет собой готовый набор IP-решений Arm, включающий в себя процессорные ядра, внутреннюю систему интерконнекта, подсистемы памяти, ввода-вывода, управлениям питанием, но оставляющий место для интеграции партнёрских разработок — различных движков, ускорителей и т.п. По сути, речь идёт о почти готовых процессорах, не требующих длительной разработки процессорной части с нуля и всех связанных с этим процессом действий — верификации, тестирования на FPGA, валидации дизайна и многого другого. По словам Arm такой подход позволяет сэкономить разработчикам до 80 человеко-лет труда инженеров. Дизайн Neoverse CSS N2 довольно гибок: финальный процессор может включать в себя от 24 до 64 ядер Arm, работающих в частотном диапазоне 2,1–3,6 ГГц. Предусмотрено по 64 Кбайт кеша инструкций и данных, а вот объёмы кешей L2 и L3 настраиваются и могут достигать 1 и 64 Мбайт соответственно. Ядра реализуют набор инструкций Arm v9 и содержат по два 128-битных векторных блока SVE2. Имеется поддержка инструкций, характерных для ИИ-задач и криптографиии. Подсистема памяти может иметь до 8 каналов DDR5, а возможности ввода-вывода включают в себя 4 блока по 16 линий PCIe или CXL. Также возможно объединение двух чипов CSS N2 в едином корпусе, что даёт до 128 ядер на чип. В качестве внутреннего интерконнекта используется меш-сеть Neoverse CMN-700. В дизайне Neoverse CSS N2 имеются и вспомогательные ядра Cortex-M7. Они работают в составе блоков System Control Processor (SCP) и Management Control Processor (MCP), то есть управляют работой основного вычислительного массива, в том числе отвечая за его питание и тактовые частоты. Инициатива Arm Total Design расширяет рамки Neoverse Compute Subsystem: речь идёт о создании полноценной экосистемы, обеспечивающей эффективную коммуникацию между партнёрами программы Neoverse CSS и предоставление им полноценного IP-инструментария и EDA, созданных при участии Cadence, Rambus, Synopsys и др. Также подразумевается поддержка ведущих производителей «кремния» и разработчиков прошивок, в частности, AMI. В число участников проекта уже вошли такие компании, как ADTechnology, Alphawave Semi, Broadcom, Capgemini, Faraday, Socionext и Sondrel. Ожидается поддержка от Intel Foundry Services и TSMC, позволяющая говорить об эффективной реализации необходимых для мультичиповых решений технологий AMBA CHI C2C и UCIe. Будучи объединённым под одной крышей инициативы Arm Total Design, такой конгломерат ведущих разработчиков и производителей микроэлектроники и системного ПО для него, сможет в кратчайшие сроки не просто создавать новые процессоры, но и гибко отвечать на вызовы рынка ЦОД и HPC, наделяя чипы поддержкой востребованных технологий и ускорителей. В качестве примера можно привести совместный проект Arm, Socionext и TSMC, в рамках которого ведётся разработка универсального чиплетного процессора, который в различных вариантах компоновки будет востребован гиперскейлерами, поставщиками инфраструктуры 5G/6G и разработчиками периферийных ИИ-систем.

18.10.2023 [13:13], Сергей Карасёв

Ampere и ещё около десяти разработчиков чипов создали ИИ-альянс AI PlatformРяд разработчиков микрочипов объявили об объединении усилий в рамках организации AI Platform Alliance с целью ускорения внедрения передовых решений в области ИИ. Инициативу возглавляет Ampere Computing, развивающая экосистему серверных процессоров с архитектурой Arm. В состав нового альянса вошли ещё около десяти компаний, большая часть из которых появилась относительно недавно: Cerebras Systems, Furiosa, Graphcore, Kalray, Kinara, Luminous, Neuchips, Rebellions и Sapeon. Ожидается, что в ближайшие месяцы список участников расширится.

Источник изображения: AI Platform Alliance Цель проекта — сделать платформы ИИ более открытыми, эффективными и устойчивыми. Усилия будут сфокусированы прежде всего на разработке передовых аппаратных решений. В частности, речь идёт о специализированных ускорителях, которые позволят решать ИИ-задачи с более высоким быстродействием и при меньшем потреблении энергии по сравнению с GPU. Ещё одной задачей группы станет оценка комплексных ИИ-платформ, основанных на совместных решениях участников альянса. Это могут быть, например, серверы, сочетающие процессоры Ampere с ускорителями машинного обучения, созданными другими членами AI Platform Alliance. В долгосрочной перспективе планируется вывести на рынок более эффективные альтернативы современным вычислительным ИИ-системам, основанным на GPU. Предполагается, что это позволит удовлетворить растущий спрос на HPC-мощности для реализации ресурсоёмких проектов в ИИ-сфере.

17.10.2023 [19:00], Алексей Степин

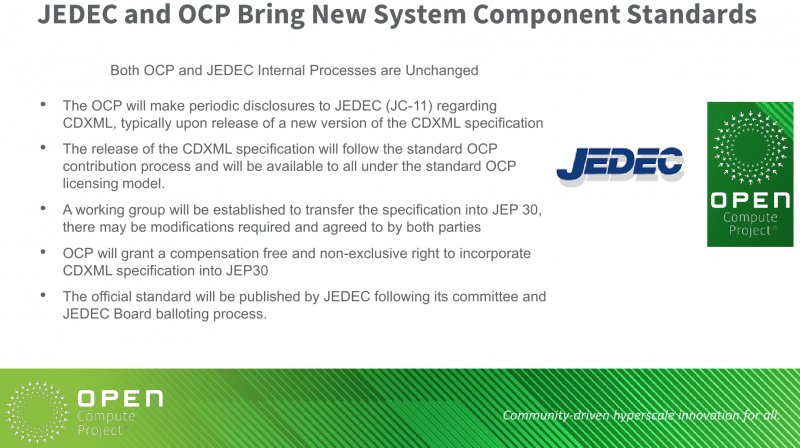

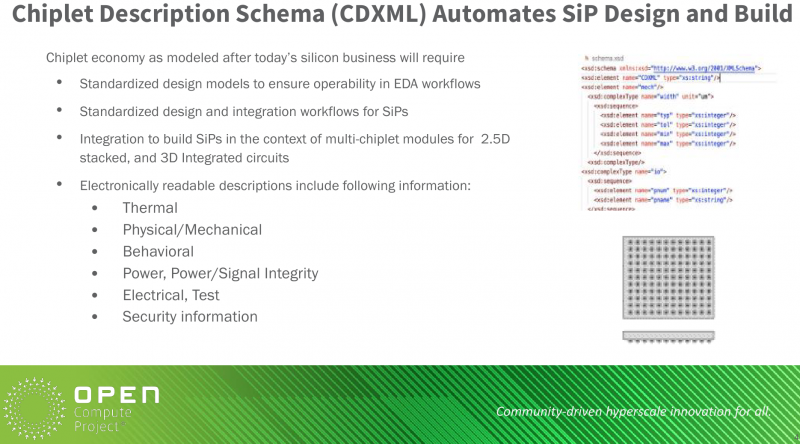

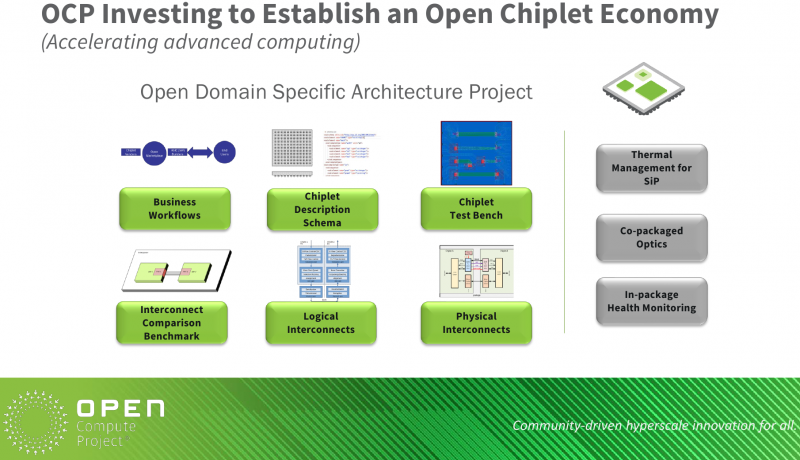

OCP и JEDEC намерены построить «чиплетную экономику»Сейчас уже очевидно, что ставка на огромные монолитные кристаллы в деле производства сложных чипов себя исчерпала и будущее за чиплетными технологиями. Но каким будет это будущее? Комитет стандартизации полупроводниковой продукции (JEDEC) и организация Open Compute Project на проходящем в настоящее время мероприятии 2023 OCP Global Summit объявили о сотрудничестве с целью выработки единого набора стандартов и унификации чиплетной экосистемы. Такой альянс способен задействовать сильнейшие стороны участников: влиятельность JEDEC в деле установления мировых стандартов в области микроэлектроники и опыт OCP в разработке устройств системного уровня, способствующий появлению новых технологий и рынков. Это позволит избежать фрагментации и излишних затрат, вызванных дублированием усилий при разработке новых устройств. OCP уже располагает спецификациями CDXML (Chiplet Data Extensible Markup Language), включающими стандартизированное описание, которое можно использовать при работе с современными средствами автоматизированного проектирования электроники (EDA). CDXML включает в себя следующие данные:

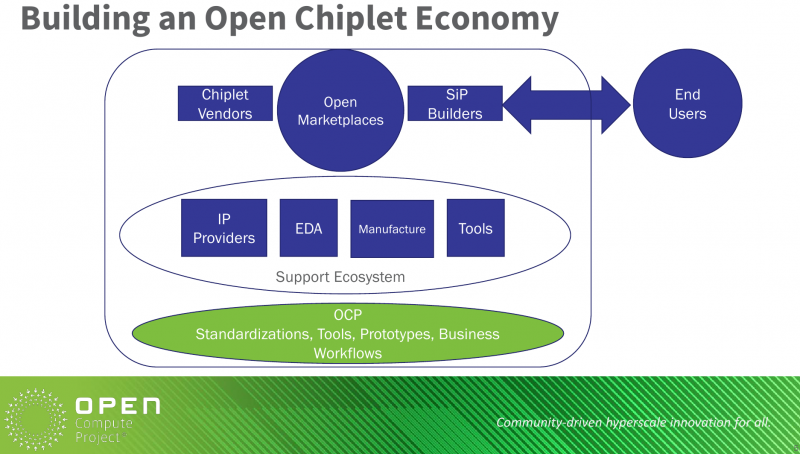

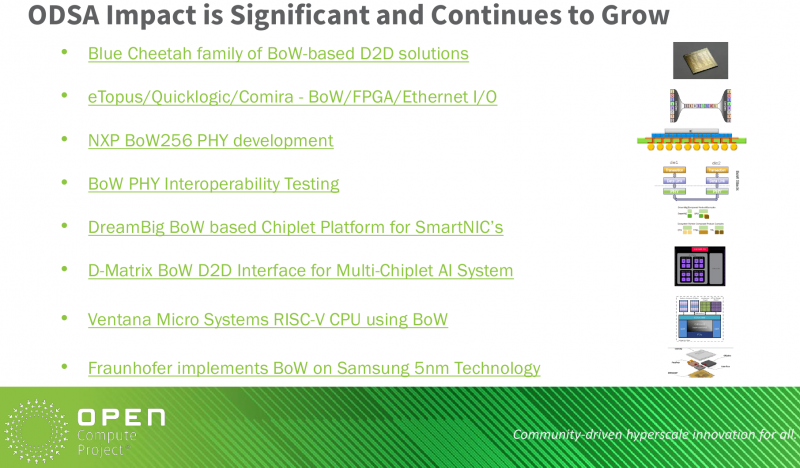

Это облегчит обмен данными между разработчиками чиплетов и их клиентами, благо уже сейчас идёт процесс интеграции CDXML в правила JEDEC JEP30 (Part Model Guidelines), описывающие процесс такого обмена. Внутренние процессы OCP и JEDEC сотрудничество не изменит, но OCP планирует регулярные поставки новых данных, относящихся к CDXML в JEDEC (JC-11) — обычно это будет связано с выпуском обновлённых версий CDXML. В соответствии с правилами лицензирования, принятыми OCP, новые данные будут доступны всем участникам консорциума. Для ускорения интеграции новых спецификаций в стандарт JEP30 будет сформирована специальная рабочая группа, в задачи которой войдёт в том числе и достижение обоюдной договорённости о внесении необходимых изменений. Официальный стандарт будет публиковаться решением комитета JEDEC в соответствии со стандартной процедурой голосования. Создание единых спецификаций CDXML открывает дорогу целому новому направлению в разработке чипов — так называемой «чиплетной экономике» (Open Chiplet Economy), в которой разработчики чиплетов смогут посредством открытого рынка взаимодействовать с производителями чипов. Такой рынок станет возможным именно благодаря созданию унифицированной экосистемы, за поддержание которой в актуальном состоянии и будет отвечать OCP. В рамках такой экономики любой проект сможет пройти от стадии описания чиплета к его тестированию с помощью специальной платформы, оценке производительности систем интерконнекта, интеграции разнородных систем, и, наконец, сборке готового решения с оценкой его термальных характеристик. Предполагается также возможность использования фотоники и наличие интегрированных средств диагностики. В рамках проекта OCP Open Domain Specific Architecture (ODSA) уже достигнуты серьёзные успехи, в число которых входит разработка высокоскоростного конфигурируемого интерконнекта Blue Cheetah класса BoW (Bunch of Wires), создание платформы DreamBig для «умных» сетевых адаптеров, использование BoW-интерконнекта в процессоре с архитектурой RISC-V и даже интеграция BoW-технологии в 5-нм техпроцесс Samsung. А сотрудничество OCP с JEDEC должно ускорить формирование «чиплетной экономики» и избежать ошибок, свойственных закрытым стандартам и платформам.

29.10.2021 [02:28], Игорь Осколков

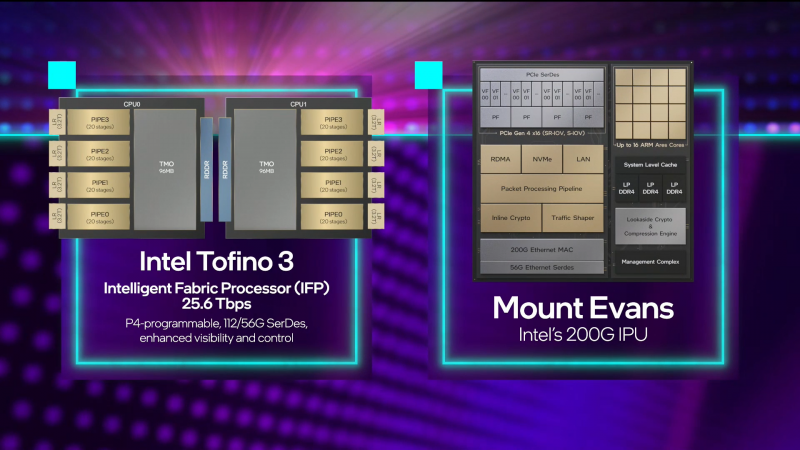

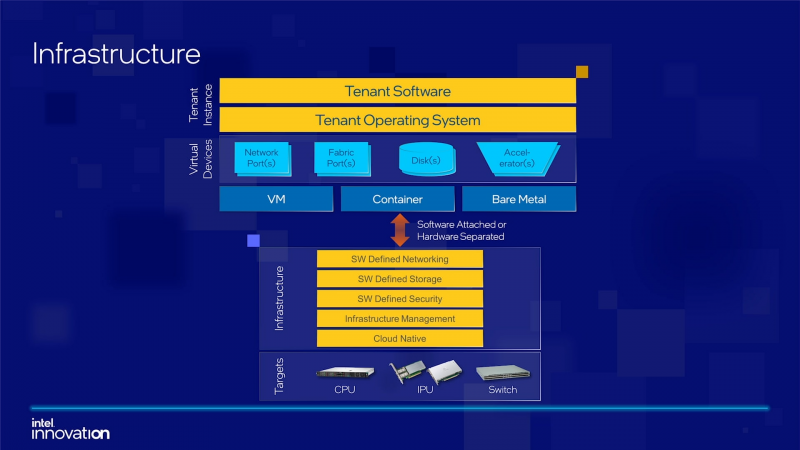

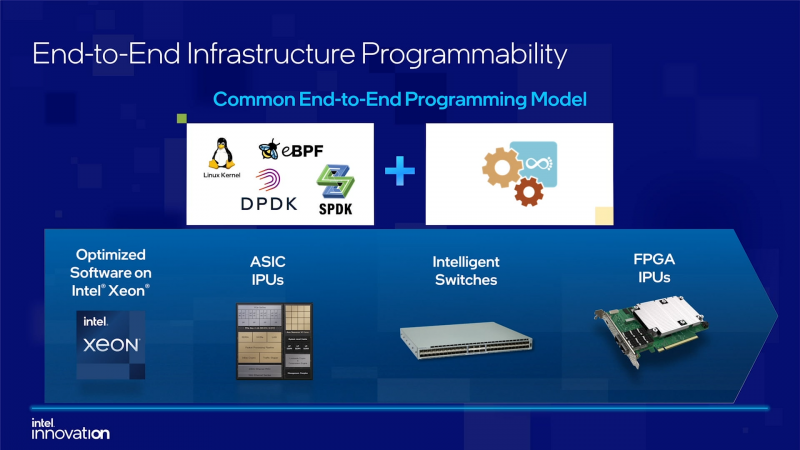

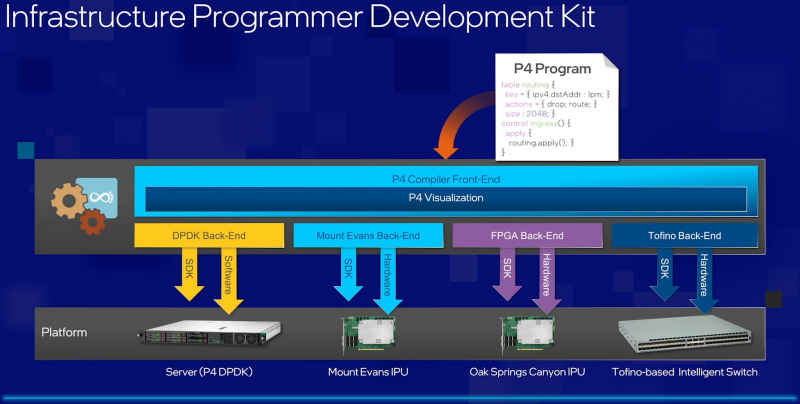

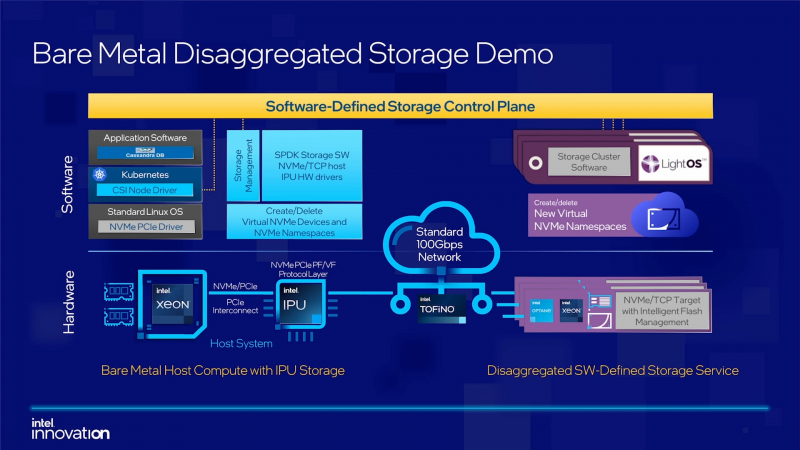

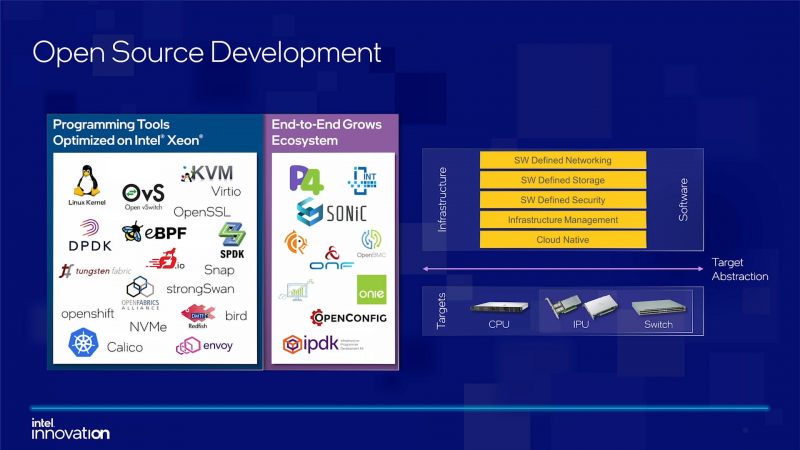

Intel объявила о совместной работе с Google над IPU Mount Evans и анонсировала IPDKIntel в рамках мероприятия Innovation раскрыла имя партнёра по разработке IPU Mount Evans — им оказалась компания Google. Впрочем, это не означает, что новинки будут доступны только ей и окажутся оптимизированы только под её задачи. IPU хоть и ориентированы в первую очередь на гиперскейлеров (среди возможных заказчиков называют и Facebook✴), но, по мнению Intel, будут интересны и менее крупным игрокам. Более того, было, наконец, прямо сказано, что ведётся работа и над Project Monterey от VMware. Как пояснил Гвидо Аппенцеллер (Guido Appenzeller), технический директор подразделения Data Platforms Group Intel, название IPU (Infrastructure Processing Unit) было выбрано в противовес всё ещё относительно новому, но более привычному термину DPU (Data Processing Unit) именно потому, что IPU охватывает более широкий спектр задач по работе именно с инфраструктурой, а не только c данными. Справедливости ради отметим, что и сами DPU, поначалу чаще ориентированные именно на ускорение работы с СХД и устранению узких мест в передаче данных, уже расширили свою функциональность и практически являются IPU именно в терминологии Intel — этот класс сопроцессоров независим от хост-системы и занимается обслуживанием инфраструктуры, включая работу с сетью и хранилищем, изоляцию и телеметрию, управление нагрузками и т.д. У Intel достаточно богатый опыт работы по сетевому направлению с гиперскейлерами. По словам Аппенцеллера, семь из восьми крупнейших компаний этого класса используют решения Intel во всей или хотя бы в некоторых частях своей инфраструктуры. Так, Microsoft, Baidu и JD полагаются на SmartNIC на базе FPGA. Партнёрство же с Google будет выгодно для обеих компаний. Intel получит заказы, а Google, наконец, обретёт то, что давно есть у Amazon — аналог Nitro. На масштабе в миллионы серверов это очень важно. Однако IPU (как аппаратные устройства) — только часть общей картины. Для полноты не хватает как минимум ещё двух компонентов: программного стека и сопутствующей инфраструктуру. Tofino-3 — анонсированный ранее чип или, как его называет сама Intel, Intelligent Fabric Processor — не только поддерживает коммутацию на скорости 25,6 Тбит/с с параллельным сбором телеметрии, но и является полностью P4-программируемым. А это позволяет организовать сквозные мониторинг, управление и оптимизацию трафика для конкретных задач. Или, иными словам, IPU и подходящие коммутаторы позволяют сделать всю инфраструктуру практически полностью программно определяемой, но с аппаратной разгрузкой части функций и близкой к bare metal итоговой производительностью. Правда, в качестве демо Intel опять же приводит «классические» примеры с СХД и Open vSwitch, а также сценарии глубокого мониторинга производительности и быстрого поиска проблемных мест в сети. Но этим потенциальные возможности не ограничиваются. Более того, со стороны ПО и средств разработки жёсткой привязки именно к «железу» Intel нет. Компания представила open source фреймворк IPDK (Infrastructure Programmer Development Kit) для упрощения переноса и, что важно, оптимизации наиболее тяжёлых или нетривиально реализуемых функций ПО на SmartNIC (с FPGA или иной программируемой логикой), IPU/DPU, коммутаторы или CPU. IPDK дополняет уже имеющиеся решения вроде DPDK, SPDK и т.д. возможностями работы с P4.

21.12.2020 [18:41], Алексей Степин

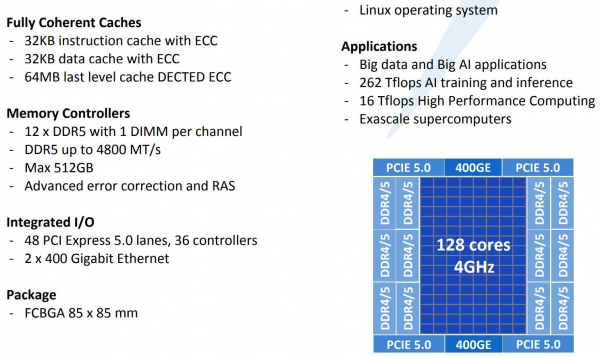

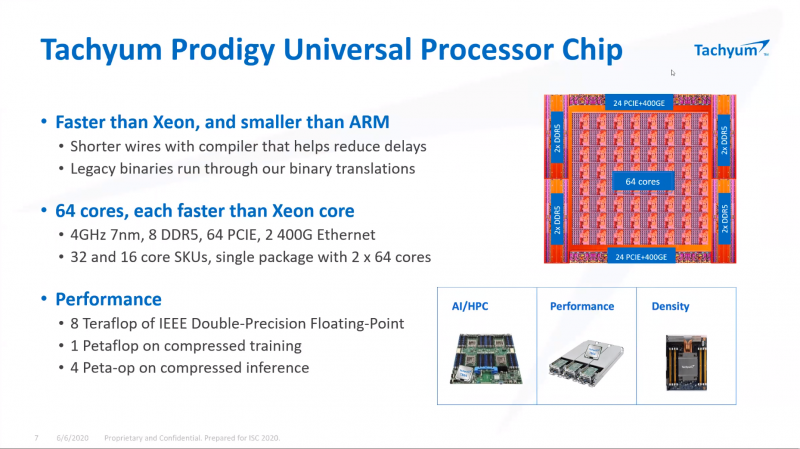

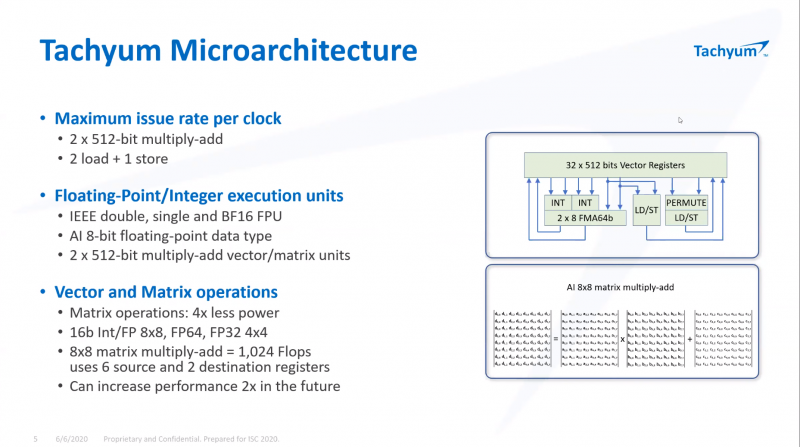

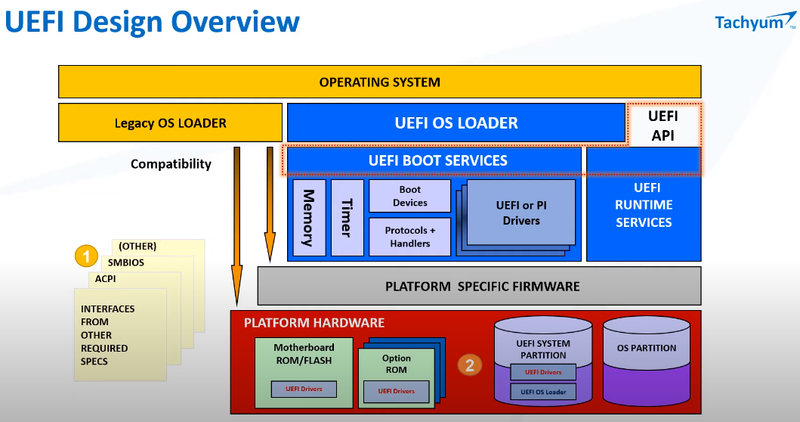

128-ядерные супепроцессоры Tachyum Prodigy стали на шаг ближе к реальностиЛетом уходящего года компания Tachyum объявила о том, что собирается отправить Xeon «на свалку истории». Сделать это должен 128-ядерный процессор нового поколения Prodigy. Хотя массово он пока не производится, компания продолжает активно работать над проектом и совсем недавно объявила начало предзаказов на эмуляторы нового процессора, как программные, так и базирующиеся на ПЛИС. Также она продемонстрировала рабочий UEFI для будущих CPU.  Молодая словацкая компания замахнулась на многое. Её процессор должен получить до 128 ядер, работающих на частоте до 4 ГГц. Чтобы «накормить» его данными, предусмотрен 12-канальный контроллер памяти DDR5. С периферией Prodigy будет общаться посредством 48 линий PCIe 5.0, но также получит и два контроллера Ethernet класса 400G. Характеристики весьма впечатляют.  Разработчики заявляют, что Prodigy найдёт своё место в системах класса Big Data и мощных системах машинного обучения. Если верить Tachyum, производительность разрабатываемого процессора должна достигнуть 16 и 8 Тфлопс на классичесих вычислениях FP32/FP64. В режиме машинного обучения и инференса возможности новой архитектуры выглядят ещё внушительнее, поскольку речь идёт о цифре 262 Тфлопс.  Столь громкие анонсы в истории вычислительной техники часто заканчивались «на бумаге», но Tachyum действительно работает над реализацией Prodigy. Как это обычно бывает, новая процессорная архитектура отрабатывается разработчиками с помощью эмуляции — как чисто программной, так и базирующейся на мощных ПЛИС. Это позволяет понять возможности и особенности поведения архитектуры, пусть и работающей с меньшей производительностью.  В начале декабря Tachyum объявила об открытии предзаказов на ПЛИС-эмулятор Prodigy, позволяющий начать разработку программного обеспечения для будущих систем на базе нового процессора уже сейчас. Поставки должны начаться в первом квартале 2021 года. В середине месяца Tachyum анонсировала и возможность заказа программного эмулятора Prodigy. Главная ценность такого эмулятора — более низкая стоимость в сравнении с вариантом на базе ПЛИС. Любой процессор неработоспособен без сопутствующего системного программного обеспечения — BIOS или, что сейчас встречается намного чаще, UEFI. В начале месяца Tachyum объявила о том, что передаст OEM и ODM-партнёрам UEFI, разработанное для новой архитектуры. При этом ПО будет поставляться не только в бинарном виде, разработчики получат и исходные коды.  К настоящему времени, таким образом, компания предлагает программные и ПЛИС-эмуляторы нового процессора, и сопутствующее программное обеспечение. К чести Tachym, разработан не только UEFI — имеется и ядро Linux с поддержкой новой архитектуры, набор средств разработки, включая компиляторы (в том числе, для ИИ-задач) и отладчики кода. Успешно продемонстрирована возможность работы на Prodigy бинарного кода, созданного для архитектур x86, ARM и RISC-V. Первые чипы Prodigy должны появиться уже в следующем году. Если запуск будет успешным, Tachym может сильно изменить привычную картину мира в сфере HPC и ИИ, ведь новая архитектура обещает быть производительнее классических Xeon и EPYC при на порядок более низком энергопотреблении, втрое более низкой стоимостью в пересчёте на MIPS, и вчетверо более низкой стоимостью владения. Более того, Prodigy угрожает даже ускорителям, обеспечивая сравнимый или более высокий уровень производительности в задачах, где последние традиционно сильны, например, в системах машинного обучения. Остаётся лишь пожелать Tachyum удачи в столь смелом начинании. |

|