Материалы по тегу: risc-v

|

31.08.2023 [13:59], Сергей Карасёв

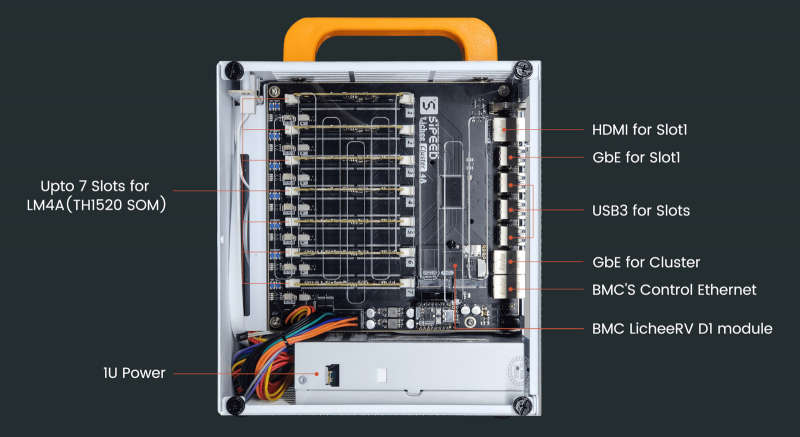

Sipeed представила кластер Lichee Cluster 4A на архитектуре RISC-VКомпания Sipeed, по сообщению CNX-Software, подготовила к выпуску компактный кластер Lichee Cluster 4A на архитектуре RISC-V. Продажи новинки, функционирующей под управлением Debian, начнутся в сентябре нынешнего года. Изделие допускает установку семи вычислительных модулей Lichee Module 4 Model A (LM4A). Они наделены чипом Xuantie C910 (RV64GCV) с четырьмя ядрами RISC-V, нейропроцессорным блоком (NPU) производительностью до 4 TOPS, энергоэффективным ядром Xuantie E902, графическим узлом Imagination 3D (50 Гфлопс) и DSP Xuantie C906. Кластер может нести на борту в сумме до 112 Гбайт оперативной памяти LPDDR4X и до 896 Гбайт флеш-памяти eMMC. Доступны семь слотов для карт microSD — по одному на модуль LM4A. В оснащение Lichee Cluster 4A входят сетевые порты 1GbE для кластера в целом и одного из разъёмов для вычислительных модулей, интерфейс HDMI, семь портов USB 3.0 и один порт USB 2.0, а также Ethernet-порт (BMC) для управления. Габариты новинки составляют 200 × 120 × 220 мм. Питание может подаваться от внутреннего блока или через DC-разъём. В верхней части устройства предусмотрена ручка для переноски. За охлаждение отвечает активная система с вентилятором, имеющим боковое расположение.

21.08.2023 [11:06], Сергей Карасёв

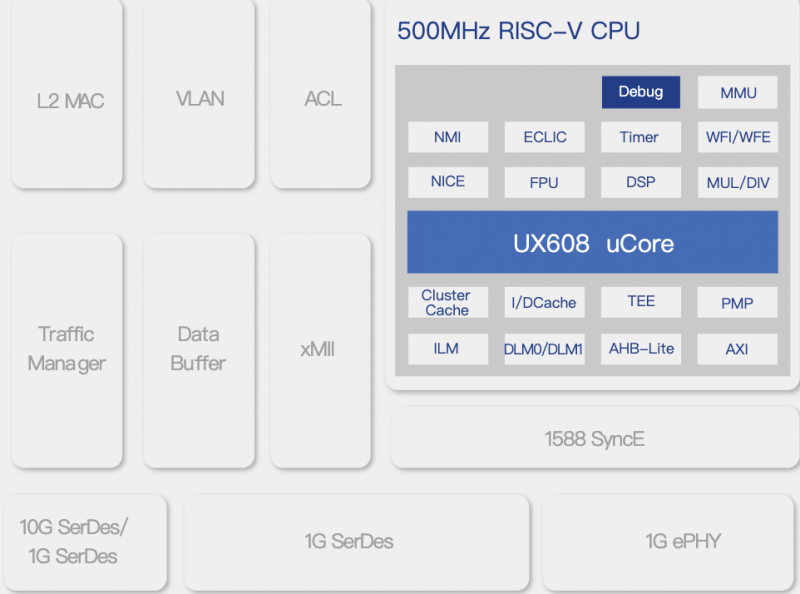

Представлен Milk-V Vega — первый в мире 10GbE-коммутатор на базе RISC-VКомпания Shenzhen MilkV Technology (Milk-V) анонсировала первый, по её словам, в мире коммутатор стандарта 10GbE на базе открытой архитектуры RISC-V. Устройство получило название Milk-V Vega: оно предназначено для применения в сетях широкополосного доступа, в составе платформ видеонаблюдения и аудиовизуальных сервисов, в системах умных городов и пр. Задействован RISC-V-чип FSL1030M разработки Wuhan Binary Semiconductor Corporation. Изделие функционирует на частоте 400 МГц и располагает кешем объм 1,5 Мбайт. В качестве программной платформы используется ОС с ядром Linux. Milk-V Vega располагает двумя портами 10GbE SFP+, четырьмя разъёмами 1GbE SFP и восемью портами 1GbE RJ-45. Возможен монтаж двух устройств в стандартную серверную стойку бок о бок. Процессорная часть основана на ядре UX608 uCore (Nuclei System Technology). Поддерживаются набор инструкций RV32/64 IMACFDPB, интерфейсы AHB-Lite, ILM/DLM и пр. Предусмотрена настраиваемая память SRAM для инструкций и данных. Конфигурация чипа включает помио кешей инструкций ICache и данных DCache ещё и Cluster Cache. Поддерживаются интерфейсы JTAG и cJTAG. Используемый в устройства китайский чип-коммутатор (L2) FSL91030M обеспечивает поддержку восьми гигабитных PHY-портов (10/100/1000BASE-T и 100BASE-FX), двух портов 10G SerDes (1000BASE-X, SGMII, QSGMII, O-USGMII и 10G BASE-R) и четырёх портов 1G SerDes (1000BASE-X и SGMII). Возможно использование четырёх комбинированных портов 1G SerDes и 1 GbE PHY. Кроме того, FSL91030M позволяет использовать два порта в качестве расширяемых интерфейсов RGMII/GMII/MII.

06.08.2023 [10:34], Сергей Карасёв

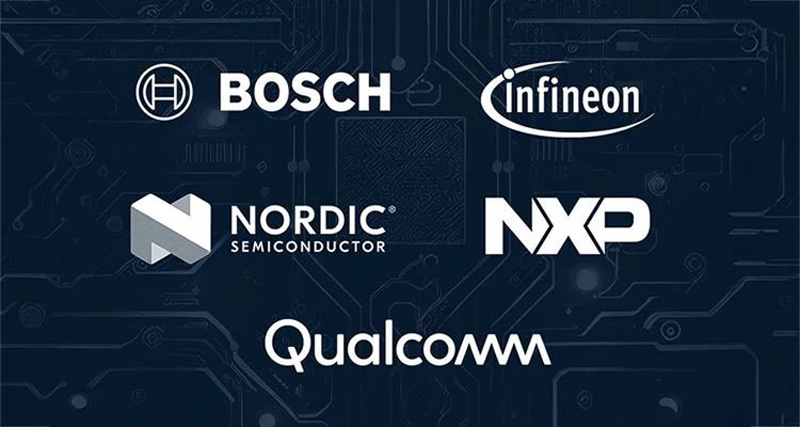

Qualcomm, NXP, Bosch, Infineon и Nordic объединили усилия для ускорения развития и внедрения RISC-VQualcomm, NXP Semiconductors, Infineon Technologies, Nordic Semiconductor и Bosch сообщили об объединении усилий с целью развития экосистемы RISC-V и продвижения продуктов на этой открытой процессорной архитектуре. Речь идёт прежде всего о разработке аппаратного обеспечения следующего поколения — сначала для автомобильной промышленности, а затем для IoT и других сфер. Участники инициативы намерены совместно инвестировать в новую компанию, которой предстоит заняться поддержкой проектов RISC-V. Название этой фирмы не раскрывается, но известно, что она будет базироваться в Германии. Новая компания, как отмечается, предоставит эталонные решения и поможет создать платформы, широко используемые в отрасли. Кроме того, совместное предприятие позволит ускорить коммерциализацию будущих продуктов на основе RISC-V.

Источник изображения: Liliputing «Дальнейшее внедрение технологии RISC-V будет способствовать ещё большему разнообразию в электронной промышленности, поможет в развитии бизнеса небольших и начинающих компаний, а также повысит масштабируемость уже существующих игроков», — говорится в совместном заявлении партнёров. На начальном этапе компания сосредоточится на решениях для автомобильной промышленности, а в перспективе планирует разрабатывать продукты для Интернета вещей (IoT) и мобильных устройств. Новая структура призывает отраслевые ассоциации, участников рынка и правительства объединить усилия в поддержку этой инициативы, которая поможет «повысить устойчивость полупроводниковой экосистемы». О размере инвестиций в проект ничего не сообщается. Нужно отметить, что Qualcomm является одним из крупнейших в мире поставщиков чипов с архитектурой Arm. Её участие в новой инициативе говорит о том, что компания намерена заняться активной разработкой изделий RISC-V.

01.08.2023 [19:22], Руслан Авдеев

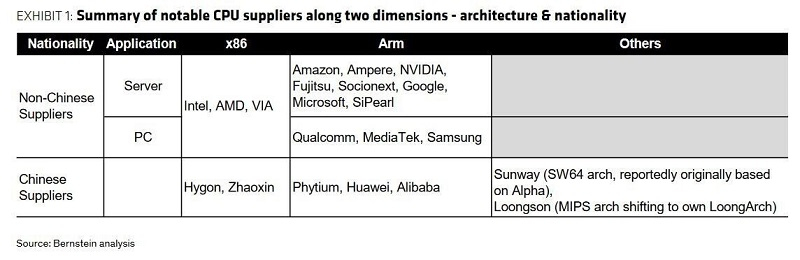

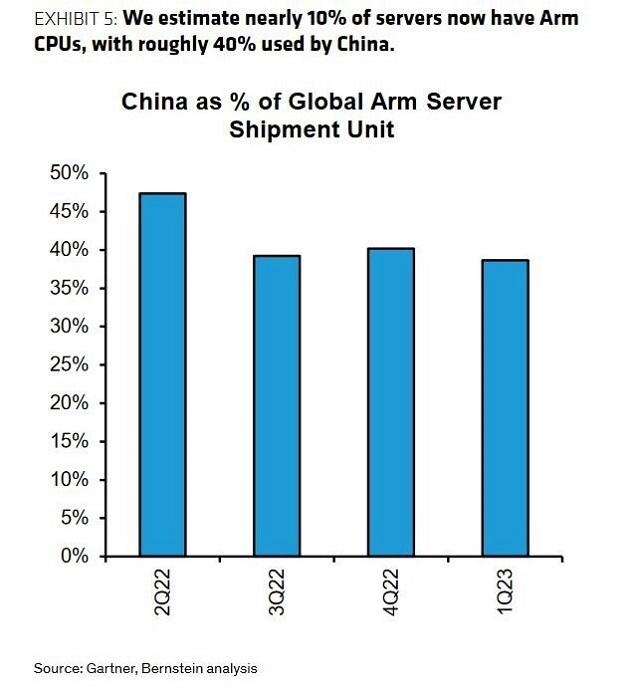

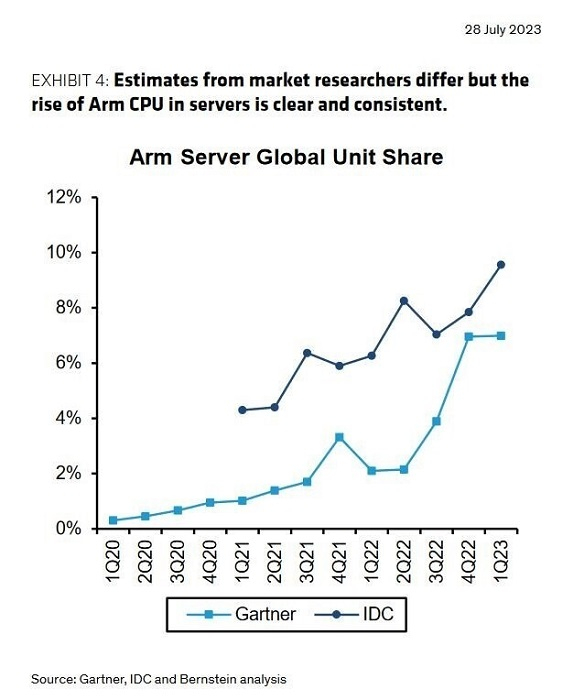

В Китае находится 40 % всех Arm-серверов мираПоскольку проблем с приобретением серверов на архитектуре x86 у китайского бизнеса всё больше из-за иностранных экспортных ограничений, китайским операторам ЦОД приходится искать обходные пути для строительства цифровой инфраструктуры. Как сообщает TechPowerUp, компании из Поднебесной ускорили переход на Arm-системы. Хотя на мировом рынке пока доминируют серверные решения на архитектуре x86, доля Arm растёт, особенно в Китае. Как сообщает инвестиционный банк Bernstein, здесь сегодня находится около 40 % всех Arm-серверов мира. Среди западных компаний чипы на Arm уже разработали и начали внедрять техногиганты AWS, Ampere, Google, Fujitsu, Microsoft и NVIDIA, однак общая доля Arm на мировом серверном рынке составляет около 10 %. В Поднебесной разработкой серверных чипов на Arm-архитектуре занимаются компании вроде Huawei, Alibaba и Phytium, хотя американские санкции влияют и на этот сектор рынка. Так, внесённые в чёрный список США Huawei и Phytium не могут размещать заказы на передовых производственных линиях TSMC, что сильно усложняет выпуск конкурентоспособных решений.

Источник изображения: Bernstein Принадлежащей Alibaba компании T-Head использование новейших техпроцессов TSMC не запрещено, но компания не может получить лицензии на использование новейшей архитектуры ядер Neoverse V, разработанной Arm, тоже из-за зарубежных экспортных ограничений.

Источник изображения: Gartner, Bernstein На этом фоне многие компании начали рассматривать RISC-V в качестве альтернативы x86 и Arm. На RISC-V не распространяются санкции иностранных регуляторов, и она активно применяется для решения ряда специализированных задач. Тем не менее, поддержка влиятельными игроками вроде AWS, Google, NVIDIA, Microsoft, Qualcomm и Samsung архитектуры Arm мешает повсеместному распространению RISC-V. Поддержка техногигантов, вероятно, и в дальнейшем обеспечит первоочередное распространение Arm на рынке дата-центров.

Источник изображения: Gartner, IDC, Bernstein Впрочем, ситуация может измениться. Известно, что RISC-V International, включающая более 1000 компаний из разных стран мира, готовится сформировать спецификации для серверных чипов и систем, утвердив стандартные аппаратные и программные интерфейсы. Это может дать технологии новое дыхание на мировом рынке.

01.08.2023 [10:02], Сергей Карасёв

Esperanto готовит универсальный чип ET-SoC-2 на базе RISC-V для задач НРС и ИИСтартап Esperanto Technologies, по сообщению ресурса HPC Wire, готовит новый чип с архитектурой RISC-V, ориентированный на системы высокопроизводительных вычислений (НРС) и задачи ИИ. Изделие получит обозначение ET-SoC-2. Нынешний чип ET-SoC-1 объединяет 1088 энергоэффективных ядер ET-Minion и четыре высокопроизводительных ядра ET-Maxion. Решение предназначено для инференса рекомендательных систем, в том числе на периферии. Чип ET-SoC-2 будет включать в себя новые высокопроизводительные ядра CPU на базе RISC-V с векторными расширениями. Точные данные о производительности не раскрываются, но говорится, что изделие обеспечит быстродействие с двойной точностью более 10 Тфлопс. Архитектура ET-SoC-2 предполагает совместную работу сотен и тысяч чипов для организации платформ НРС. При этом Esperanto делает упор на энергетической эффективности своих решений.

Источник изображения: Esperanto Technologies По словам Дейва Дитцеля (Dave Ditzel), генерального директора Esperanto, чипы RISC-V смогут взять на себя функции и CPU, и GPU при обработке ресурсоёмких приложений, в частности, машинного обучения. Процессоры RISC-V отстают по производительности от чипов x86 и Arm, хотя разрыв постепенно сокращается. Дитцель сказал, что стойки с чипами ET-SoC-1 могут обеспечить производительность в петафлопсы. Однако проблема с внедрением RISC-V заключается в слабо развитой экосистеме ПО.

25.07.2023 [17:12], Руслан Авдеев

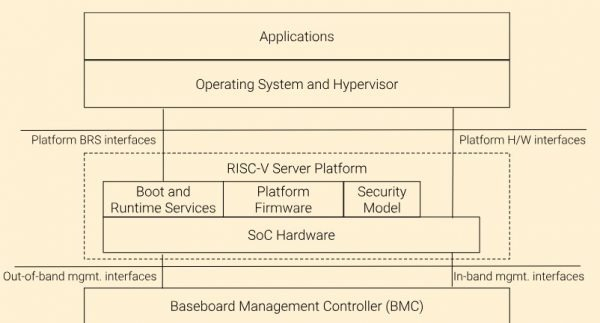

RISC-V International стандартизирует серверные чипы на архитектуре RISC-VRISC-V International, включающая более 1000 компаний из разных стран мира и ставшая ключевым игроком в сфере разработки чипов на архитектуре RISC-V, готовит новый проект. Как сообщает HPC Wire, организация готовится сформировать спецификации для серверных чипов и систем. В частности, речь идёт об утверждении стандартных аппаратных и программных интерфейсов. Ожидается, что появление таких стандартов позволит применять серверы с решениями на основе RISC-V в облачных средах, где ПО часто виртуализировано. Пока разработка спецификаций касается преимущественно дополнительных компонентов вроде системных контроллеров, уровней виртуализации, систем загрузки, безопасности и т.п. Также спецификация определяет набор возможностей, доступных системному ПО вроде операционных систем и гипервизоров. Кроме того, в новых спецификациях будет прописана поддержка серверными решениями на такой архитектуре технологий вроде CXL.

Источник изображения: RISC-V International Многие компании уже разрабатывают серверные RISC-V чипы, например, Ventana и Esperanto. Они создают собственные решения, дополняя базовую архитектуру, но они также выразили готовность следовать новым стандартам RISC-V International. Впрочем, пока RISC-V всё ещё не рассматривается как равноценная альтернатива давно применяемым в серверных решениях вариантам x86 или Arm. Ставку на её развитие делают многие компании, включая AMD, Apple, Intel, NVIDIA и Qualcomm, а также российские и китайские компании, страдающие от санкционного давления.

24.07.2023 [17:16], Руслан Авдеев

Российская UDV Group анонсировала первый отечественный межсетевой экран на базе RISC-VUDV Group, российский разработчик решений в сфере кибербезопасности для промышленных и корпоративных клиентов представил первый, по его словам, в стране межсетевой экран, использующий архитектуру RISC-V. Как сообщает пресс-служба UDV, рабочий прототип UDV Industrial Firewall продемонстрировали на конференции IT IS conf в Екатеринбурге. Считается, что это уникальное для отечественного рынка ИБ-систем решение. UDV Industrial Firewall ориентирован на использование в промышленных сетях и предусматривает аппаратное ускорение обработки трафика. Он предназначен для разграничения доступа к сегментам сетей АСУ ТП с учётом режимов их работы и для глубокой фильтрации промышленных протоколов. В текущем квартале новинка будет тестироваться в сетях заказчиков, а в серийное производство она должна поступить во II квартале 2024 года. Пока фильтрация трафика осуществляется на скоростях до 1 Гбит/с, чего, как утверждают разработчики, вполне достаточно для промышленных сетей. Впрочем, в будущем в компании обещают поднять максимальную скорость до 40 Гбит/с благодаря использованию недорогих FPGA. Масштабировать функциональность планируется простым добавлением новых модулей расширения, способных на параллельную обработку трафика.

Источник изображения: UDV Group В компании подчеркнули, что использование RISC-V обусловлено тем, что архитектура «не является проприетарной, а также устойчива к санкционным рискам». В UDV Group заявили, что используют процессоры китайского производства, не подпадающие под санкции, и уверены, что будущее на рынке российских процессоров за решениями на архитектуре RISC-V.

24.07.2023 [15:02], Сергей Карасёв

В Debian появилась официальная поддержка архитектуры RISC-VУчастники проекта Debian сообщили о том, что редакция данной платформы для систем на основе 64-бит архитектуры RISC-V (riscv64) получила официальный статус. Иными словами, RISC-V теперь считается официальной архитектурой Debian, хотя поддержка соответствующих аппаратных решений присутствует в ОС достаточно давно. Для RISC-V обеспечена сборка приблизительно 96 % от общего количества пакетов в репозиториях Debian. Отмечается, что интеграция порта с официальным архивом Debian будет проводиться постепенно. В настоящее время присутствуют лишь экспериментальные наборы ПО.

Источник изображения: Debian На следующем этапе планируется собрать минимальный набор из примерно 90 пакетов на базе debian-ports, а затем перенести их в официальный архив. Эти пакеты будут подписаны специальным ключом GPG с использованием адреса электронной почты debian-riscv@lists.debian.org для упрощения отслеживания. Соответствующий процесс уже начался. В дальнейшем публикация сборок будет переведена на официальный архив. Пакеты с поддержкой архитектуры RISC-V доступны для установки из репозитория Debian Sid.

11.07.2023 [12:36], Сергей Карасёв

«Байкал Электроникс», возможно, начнёт разработку микроконтроллеровРоссийская компания «Байкал Электроникс», разработчик процессоров Baikal, намерена расширить продуктовый ассортимент. Как сообщает газета «Коммерсантъ», речь идёт о выпуске специализированных микроконтроллеров. Предполагается, что такие изделия найдут применение в различных сферах. «Байкал Электроникс» ищет специалистов для создания микроконтроллеров. В частности, на портале поиска работы HH опубликованы вакансии «инженера — программиста микроконтроллеров» и «ведущего программиста микроконтроллеров». Специалистам в числе прочего предстоит разработать архитектуру ПО для микроконтроллеров, программные модули и протоколы взаимодействия периферийных устройств. В «Байкал Электроникс» заявляют, что «вакансии открыты как по текущим проектам, так и по новым направлениям, которые рассматриваются в качестве возможных векторов для продуктового развития».

Источник изображения: «Байкал Электроникс» По имеющейся информации, «Байкал Электроникс» займётся разработкой микроконтроллеров для аппаратуры гражданского назначения. Это могут быть всевозможные счётчики, устройства IoT и пр. По всей видимости, в основу изделий ляжет открытая архитектура RISC-V. Заказ на производство новой продукции «Байкал Электроникс» может разместить на китайских заводах. При этом два года назад владелец «Байкал электроникс» купил долю разработчика RISC-V решений Cloudbear. Однако участники рынка полагают, что «Байкал Электроникс» может столкнуться с серьёзной конкуренцией — разработкой микроконтроллеров занимается целый ряд крупных российских компаний, включая «Микрон» и «Миландр». В частности, в ноябре 2022 года стало известно, что «Микрон» вложит 300 млн руб. в выпуск микроконтроллеров на базе RISC-V для устройств IoT.

27.01.2023 [23:32], Владимир Мироненко

На фоне колоссальных потерь прибыли Intel отказалась от развития коммутаторов и по-тихому закрыла программу Pathfinder для RISC-VКомпания Intel опубликовала итоги работы в IV квартале 2022 года, окончившемся 31 декабря и принёсшем ей значительные убытки. Выручка компании составила $14,04 млрд, что на 32 % ниже результата за аналогичный период предыдущего года, а также меньше прогноза аналитиков. Intel завершила квартал с чистыми убытками в размере $661 млн (GAAP), в то время как годом ранее её квартальная прибыль составила $4,62 млрд. В IV квартале группа клиентских решений Intel Client Computing Group (CCG) принесла доход в размере $6,63 млрд, что на 36 % ниже результата IV квартала 2021 года. Как сообщает Intel, падение спроса на ПК в основном коснулось потребительского и образовательного рынков, и клиенты решили сократить запасы на складах. По данным Gartner, рынок ПК за отчётный период сократился сильнее, чем в любом другом квартале, с тех пор как компания начала проводить мониторинг отрасли в 1990-х годах.

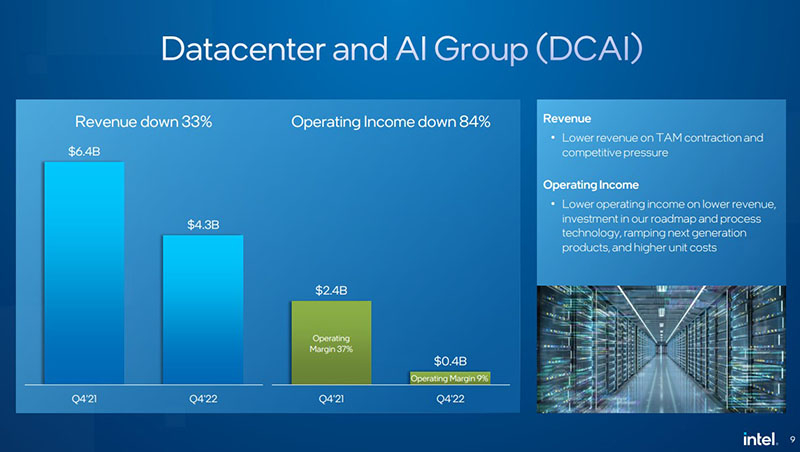

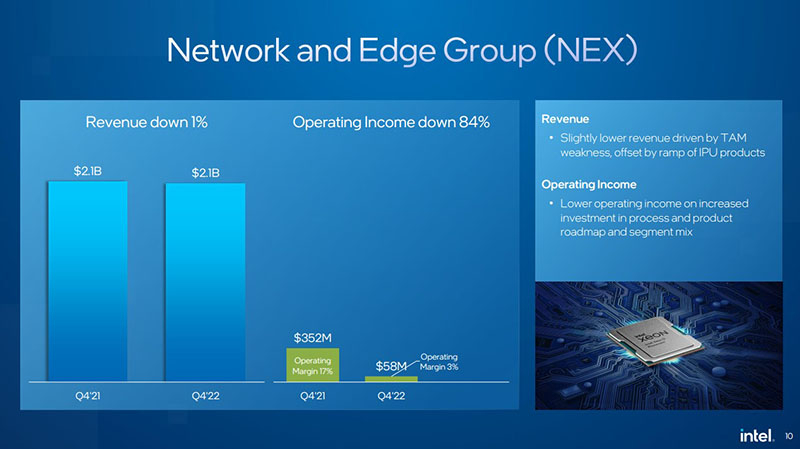

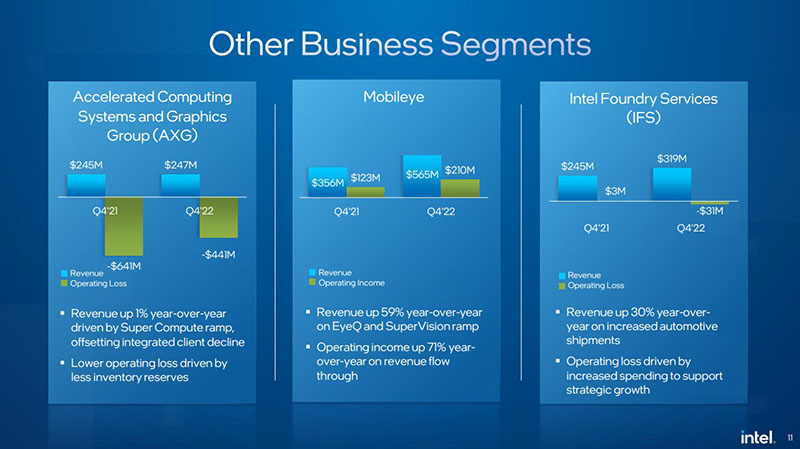

Источник изображений: Intel Группа Datacenter and AI Group (DCAI), которая отвечает за решения для ЦОД и платформы ИИ, принесло компании за квартал доход в размере $4,3 млрд, что на 33 % меньше прошлогоднего, но все же больше прогноза аналитиков. Intel объяснила результат давлением со стороны конкурентов и сокращением размера рынка. Как отметил ресурс The Register, несмотря на запуск в начале этого месяца чипов Xeon Sapphire Rapids (это первые новые CPU для ЦОД от Intel почти за два года), они только сейчас начали поступать к клиентам, включая Dell, Google Cloud, HPE, Lenovo, NVIDIA, Supermicro. То есть Intel вряд ли получит достаточно большую выручку от их реализации в этом квартале. Заодно компания решила не строить лабораторию по развитию решений для ЦОД. Всё это сыграет на руку AMD.  Группа Network and Edge Group (NEX), специализирующаяся на сетевых продуктах и периферийных вычислениях, тоже продемонстрировало признаки замедления спроса в IV квартале. Выручка группы снизилась на 1 % в годовом исчислении (до $2,1 млрд), что означает отход от тенденции к росту, о котором она сообщала в предыдущие кварталы. Впрочем, у группы в финансовом году отмечен рост дохода на 11 %. Тем не менее, компания решила фактически избавиться от бизнеса по производству коммутаторов, хотя всего несколько лет назад она инвестировала в это направление и купила Barefoot Networks. Intel сохранит поддержку текущих решений Tofino, но в дальнейшем сосредоточится на развитии IPU. При этом нельзя не отметить, что коммутаторы являлись важной частью будущей экосистемы IPU/DPU.  Положительным моментом для Intel в IV квартале 2022 года является то, что более мелкие подразделения компании показали рост. Выручка подразделения Accelerated Computing Systems and Graphics (AXG), занимающегося разработкой ускорителей, увеличило выручку на 1 % до $247 млн, а также сократило операционные убытки. Подразделение Mobileye, поставщик решений для автономного вождения, которое недавно провело IPO, принесло компании $565 млн, что больше прошлогоднего результата на 59 %. У подразделения Intel Foundry Services выручка в IV квартале выросла на 30 % до $319 млн. При этом компания без объявления закрыла программу Pathfinder for RISC-V. Кроме того, в 2022 году Intel отказалась от развития 3D XPoint/Optane.  Если говорить о результатах за год, то общая выручка Intel снизилась на 20 % (до $63,1 млрд), это привело к падению чистой прибыли на 60 % (до $8 млрд). В частности, выручка группы DCAI упала на 15 % (до $19,2 млрд), группа NEX принесла компании $8,9 млрд, что на 11 % меньше, чем в предыдущем году. Клиентская группа CCG сократила выручку в годовом исчислении на 23 % (до $31,7 млрд). Согласно прогнозу Intel, в I квартале 2023 года выручка будет примерно на 40 % ниже, чем в I квартале 2022 года, в пределах от $10 до $11,5 млрд. Валовая прибыль Intel будет находиться на уровне 39 %. |

|