Материалы по тегу: esperanto

|

06.07.2025 [00:44], Владимир Мироненко

Esperanto, создатель уникального тысячеядерного RISC-V-ускорителя, закрывается — всех инженеров переманили крупные компанииСтартап Esperanto, специализирующийся на разработке серверных ускорителей на базе архитектуры RISC-V, сворачивает свою деятельность, сообщил ресурс EE Times. В настоящее время компания, которую уже покинуло большинство сотрудников, ищет покупателя на свои технологии или заинтересованных в лицензировании её разработок. Компания известна созданием тысячеядерного ИИ-ускорителя ET-SoC-1. Генеральный директор Esperanto Арт Свифт (Art Swift) сообщил EE Times о закрытии дочерних предприятий в Европе — у неё была значительная инженерная команда в Испании и ещё одна небольшая в Сербии. В штаб-квартире Esperanto в Маунтин-Вью (Калифорния) численность персонала сократилась на 90 %. Свифт и еще несколько инженеров остались, чтобы продать или лицензировать разработки компании и содействовать любой потенциальной передаче технологий. По словам Свифта, компания подверглась атаке со стороны богатых конкурентов, которые предлагали зарплату «в два, три, даже в четыре раза выше», чем могла предложить небольшая Esperanto. «Они фактически уничтожили наши команды — очень жаль, но мы не смогли конкурировать с ними», — говорит Свифт, отмечая, что уже несколько компаний проявило интерес к приобретению технологии или её лицензированию на неисключительной основе. Он добавил, что у Esperanto был крупный клиент, которому есть что предложить, что добавляет оптимизма. Ранее компания, судя по всему, пыталась предложить свои чипы Meta✴.

Источник изображения: Esperanto Technologies Интерес рынка к RISC-V для чипов ЦОД остаётся высоким, особенно в Европе, где инвестирует в новую экосистему чипов на основе RISC-V. Вместе с тем именно ключевое преимущество разработок Esperanto — энергоэффективность — оказалось труднореализуемым, говорит гендиректор: «При неограниченном бюджете на электроэнергию энергоэффективность на самом деле не имеет значения». Esperanto готовила к выпуску чиплет второго поколения, который должен был поступить в производство на мощностях Samsung по 4-нм техроцессу в 2026 году. Чиплет предложил бы до 16 Тфлопс в FP64-вычислениях или до 256 Тфлопс в FP8-расчётах при потреблении 15–60 Вт. В один чип можно объединить до восьми чиплетов. Третье поколение технологии удвоило бы вычислительную мощность чиплетов. «Компании действительно были заинтересованы в получении этой технологии, так что посмотрим», — говорит Свифт. В прошлом году Esperanto договорилась с корпорацией NEC о сотрудничестве в области НРС с целью создания программных и аппаратных решений следующего поколения с архитектурой RISC-V. Также сообщалось о разработке чипа ET-SoC-2 для НРС и ИИ-задач. На пике развития штат Esperanto составлял 140 человек. По словам Свифта, 95 % бывших сотрудников стартапа уже нашли новую работу. В аналогичной ситуации оказалась Codasip, объявившая о готовности продать свои активы, поскольку обострение конкуренции на рынке RISC-V и отсутствие достаточного запаса средств ограничивают возможности небольших компаний, которые зачастую не могут конкурировать с IT-гигантами. ИИ-стартап Untether AI тоже провалил тест на выживание, объявив о закрытии бизнеса после того, как AMD переманила ряд его ведущих специалистов.

19.11.2024 [11:47], Сергей Карасёв

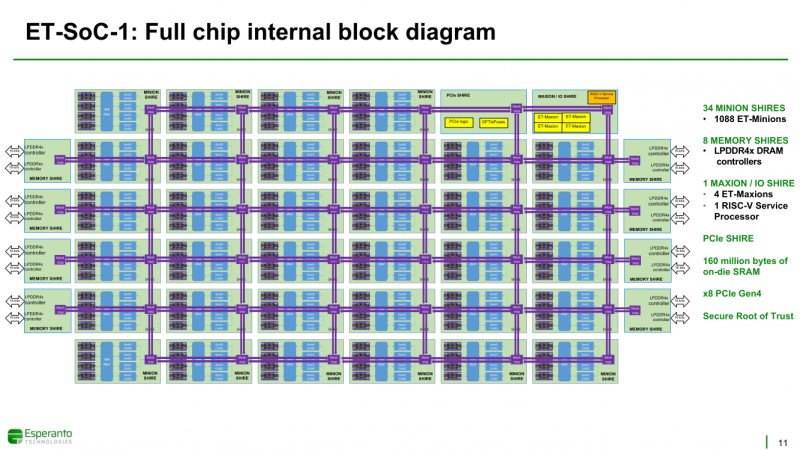

Esperanto и NEC займутся созданием HPC-решений на базе RISC-VСтартап Esperanto Technologies и корпорация NEC объявили о заключении соглашения о сотрудничестве в области НРС. Речь идёт о создании программных и аппаратных решений следующего поколения, использующих открытую архитектуру RISC-V. Напомним, Esperanto разрабатывает высокопроизводительные RISC-V-чипы для задач НРС и ИИ. Первым продуктом компании стало изделие ET-SoC-1, которое объединяет 1088 энергоэффективных ядер ET-Minion и четыре высокопроизводительных ядра ET-Maxion. Решение предназначено для инференса рекомендательных систем, в том числе на периферии. В августе 2023 года стало известно о подготовке чипа ET-SoC-2 с высокопроизводительными ядрами RISC-V с векторными расширениями. В рамках соглашения о сотрудничестве, как отмечается, будут объединены опыт и экспертизы NEC в области проектирования суперкомпьютеров и создания специализированного софта для HPC-задач с технологиями Esperanto в сфере высокопроизводительных энергоэффективных чипов на основе набора инструкций RISC-V. При этом упоминаются достижения NEC по направлению векторных процессоров: японская компания проектировала уникальные изделия SX-Aurora, но их разработка была остановлена в 2023 году.

Источник изображения: Esperanto «Используя глубокий опыт и экспертные знания NEC в области HPC, а также открытый набор инструкций RISC-V в сочетании с вычислительной технологией Esperanto, мы сможем разрабатывать масштабируемые и эффективные решения для ИИ и высокопроизводительных вычислений», — отметил Арт Свифт (Art Swift), президент и генеральный директор Esperanto.

26.08.2021 [03:07], Алексей Степин

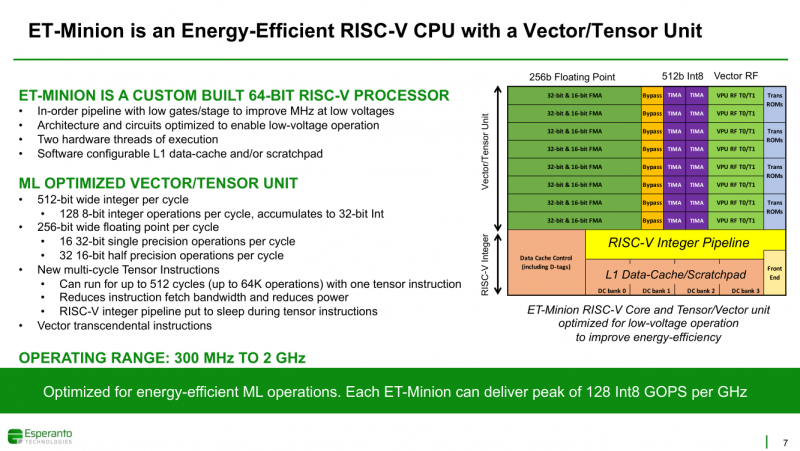

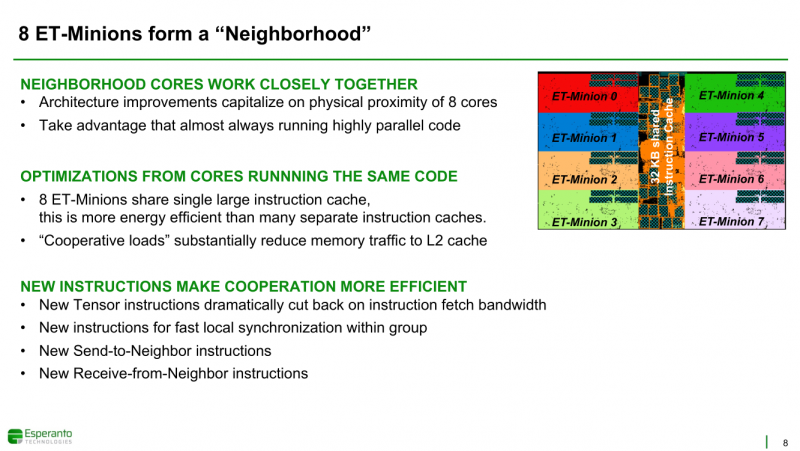

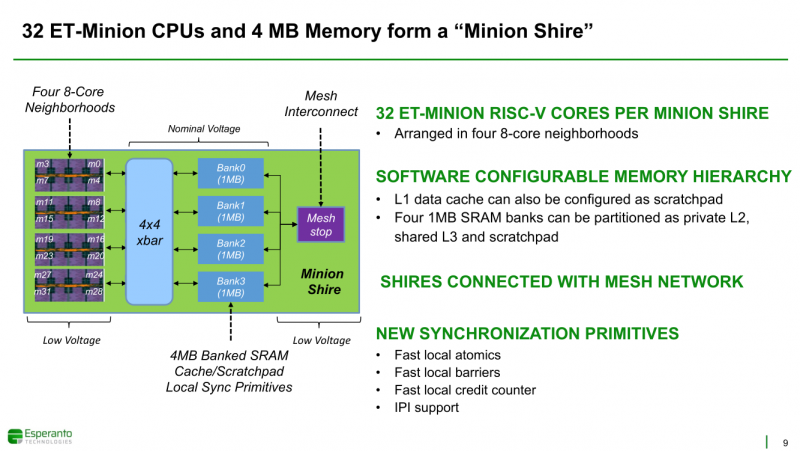

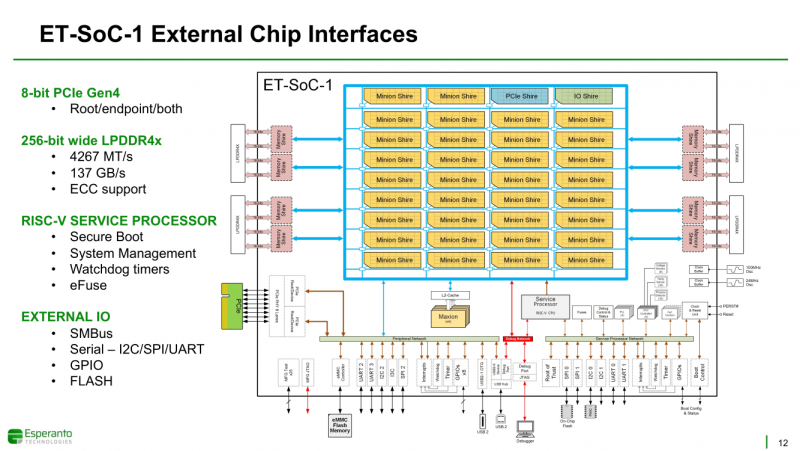

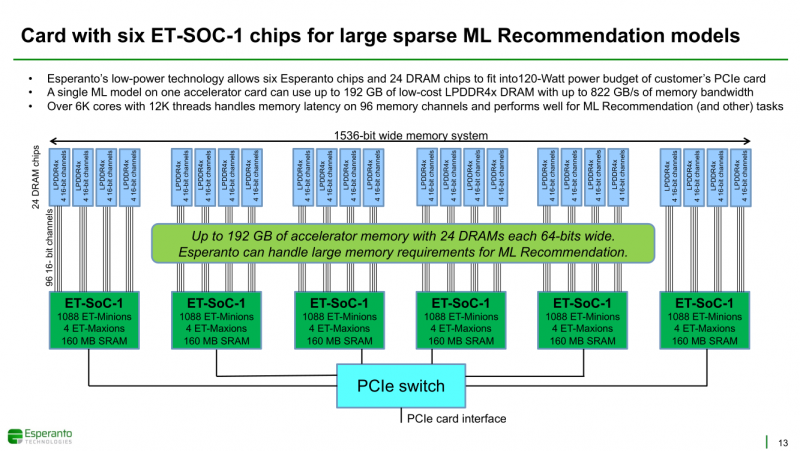

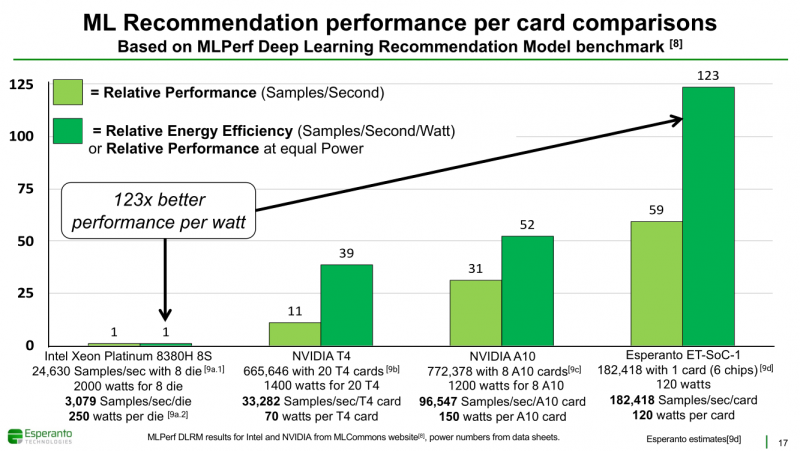

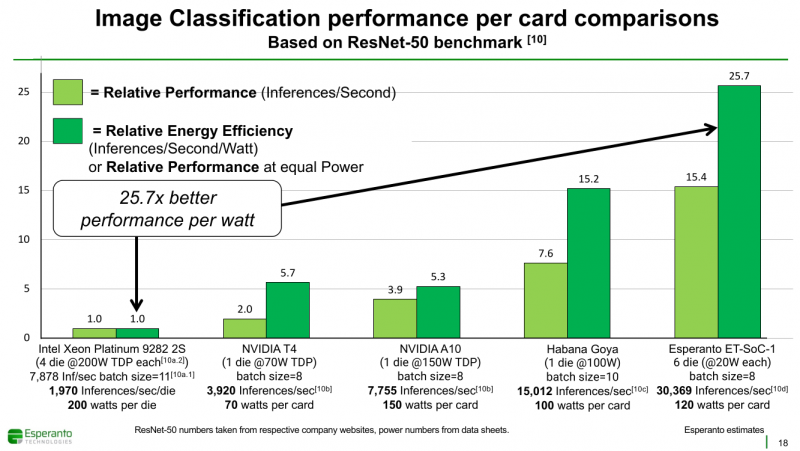

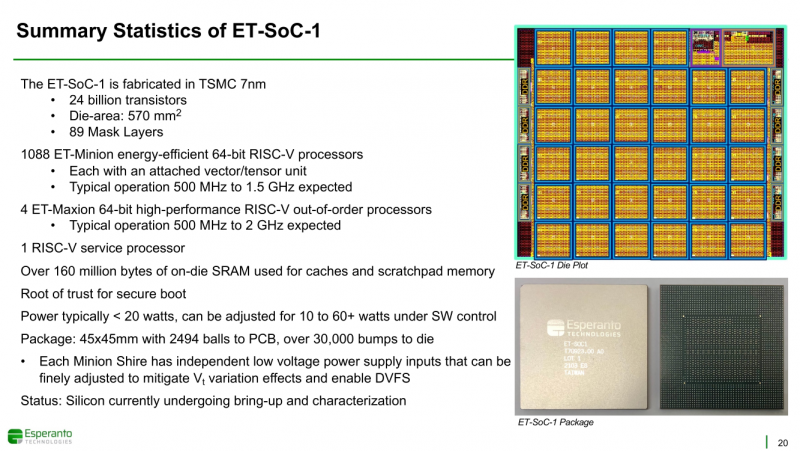

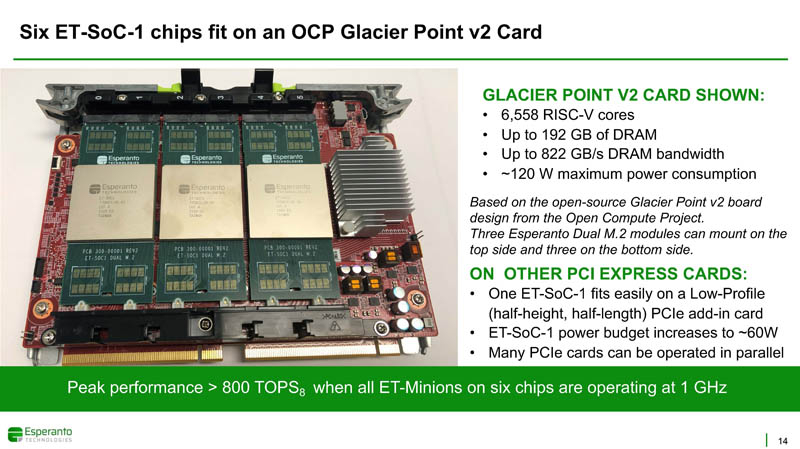

Получены первые образцы 1000-ядерного суперкомпьютера-на-чипе Esperanto ET-SoC-1Рекомендательные системы, активно используемые социальными сетями, рекламными платформами и т.д. имеют специфические особенности. От них требуется высокая скорость отклика, но вместе с тем их ИИ-модели весьма объёмны, порядка 100 Гбайт или более. А для их эффективной работы нужен ещё и довольно большой кеш. Для инференса чаще всего используется либо CPU (много памяти, но относительно низкая скорость) или GPU (высокая скорость, но мало памяти), но они не слишком эффективны для этой задачи. При этом существуют ещё и физические ограничения со стороны гиперскейлеров: в сервере не так много полноценных PCIe-слотов и свободного места + есть жёсткие ограничения по энергопотреблению и охлаждению (чаще всего воздушному). Всё это было учтено компанией Esperanto, чьей специализацией является разработка чипов на базе архитектуры RISC-V. На днях она получила первые образцы ИИ-ускорителя ET-SoC-1, который она сама называет суперкомпьютером-на-чипе (Supercomputer-on-Chip).  Новинка предназначена для инференса рекомендательных систем, в том числе на периферии, где на первый план выходит экономичность. Компания поставила для себя непростую задачу — весь комплекс ускорителей с памятью и служебной обвязкой должен потреблять не более 120 Вт. Для решения этой задачи пришлось применить немало ухищрений. Самое первое и очевидное — создание относительно небольшого, но универсального чипа, который можно было бы объединять с другими такими же чипами с линейным ростом производительности. Для достижения высокой степени параллелизма основой такого чипа должны стать небольшие, но энергоэффективные ядра. Именно поэтому выбор пал на 64-бит ядра RISC-V, поскольку они «просты» не только с точки зрения ISA, но и по транзисторному бюджету. Чип ET-SoC-1 сочетает в себе два типа ядер RISC-V: классических «больших» ядер (ET-Maxion) с внеочередным выполнением у него всего 4, зато «малых» ядер (ET-Minion) с поддержкой тензорных и векторных вычислений — целых 1088. На комплекс ядер ET-Maxion возлагаются задачи общего назначения и в ИИ-вычислениях он напрямую не участвует, зато позволяет быть ET-SoC-1 полностью автономным, так как прямо на нём можно запустить Linux. Помогает ему в этом ещё один служебный RISC-V процессор для периферии. А вот ядра ET-Minion довольно простые: внеочередного исполнения инструкций в них нет, зато есть поддержка SMT2 и целый набор новых инструкций для INT- и FP-операций с векторами и тензорами. За каждый такт ядро ET-Minion способно выполнять 128 INT8-операций с сохранением INT32-результата, 16 FP32-операций или 32 — FP16. «Длинные» тензорные операции могут непрерывно исполняться в течение 512 циклов (до 64 тыс. операций), при этом целочисленные блоки в это время отключаются для экономии питания. Система кешей устроена несколько непривычным образом. На ядро приходится 4 банка памяти, которые можно использовать как L1-кеш для данных и как быструю универсальную память (scratchpad). Восемь ядер ET-Minion формируют «квартал» вокруг общего для них кеша инструкций, так как на таких задачах велика вероятность того, что инструкции для всех ядер действительно будут одни и те же. Кроме того, это энергоэффективнее, чем восемь индивидуальных кешей, и позволяет получать и отправлять данные большими блоками, снижая нагрузку на L2-кеш. Восемь «кварталов» формируют «микрорайон» с коммутатором и четырьмя банками SRAM объёмом по 1 Мбайт, которые можно использовать как приватный L2-кеш, как часть общего L3-кеша или как scratchpad. Посредством mesh-сети «микрорайоны» общаются между собой и с другими блоками: ET-Maxion, восемь двухканальных контроллеров памяти, два root-комплекса PCIe 4.0 x8, аппаратный RoT. Суммарно на чип приходится порядка 160 Мбайт SRAM. Контроллеры оперативной памяти поддерживают модули LPDDR4x-4267 ECC (256 бит, до 137 Гбайт/с). Тактовая частота ET-Minion варьируется в пределах от 500 МГц до 1,5 ГГц, а ET-Maxion — от 500 МГц до 2 ГГц. В рамках OCP-блока Glacier Point V2 компания объединила на одной плате шесть ET-SoC-1 (всего 6558 ядер RISC-V), снабдив их 192 Гбайт памяти (822 Гбайт/с) — это больше, нежели у NVIDIA A100 (80 Гбайт). Такая связка развивает более 800 Топс, требуя всего 120 Вт. В среднем же она составляет 100 ‒ 200 Топс на один чип с потреблением менее 20 Вт. Это позволяет создать компактный M.2-модуль или же наоборот масштабировать систему далее. Шасси Yosemite v2 может вместить 64 чипа, а стойка — уже 384 чипа. В тесте MLPerf для рекомендательных систем производительность указанной выше связки из шести чипов в пересчёте на Ватт оказалась в 123 раза выше, чем у Intel Xeon Platinum 8380H (250 Вт), и в два-три раза выше, чем у NVIDIA A10 (150 Вт) и T4 (70 Вт). В «неудобном» для чипа тесте ResNet-50 разница с CPU и ускорителем Habana Goya уже не так велика, а вот с решениями NVIDIA, напротив, более заметна. При этом о поддержке со стороны ПО разработчики также подумали: чипы Esperanto могут работать с широко распространёнными фреймворками PyTorch, TensorFlow, MXNet и Caffe2, а также принимать готовые ONNX-модели. Есть и SDK для C++, а также драйверы для x86-хостов. Опытные образцы изготовлены на TSMC по 7-нм техпроцессу. Кристалл площадью 570 мм2 содержит 24 млрд транзисторов. Чип имеет упаковку BGA2494 размерами 45 × 45 мм2. Энергопотребление (а вместе с ним и производительность) настраивается в диапазоне от 10 до 60+ Ватт. Потенциальным заказчикам тестовые чипы станут доступны до конца года. Компания также готова адаптировать ET-SoC-1 под другие техпроцессы и фабрики, но демо на базе OCP-платформы и сравнение с Cooper Lake — это недвусмысленный намёк для Facebook✴, что Esperanto будет рада видеть её в числе первых клиентов. |

|