Материалы по тегу: risc-v

|

24.12.2024 [15:41], Сергей Карасёв

Sipeed выпустила NanoKVM-PCIe — плату расширения IP-KVM с OLED-дисплеем и Wi-Fi 6Компания Sipeed анонсировала решение NanoKVM-PCIe — плату расширения с интерфейсом PCIe для организации удалённого управления IP-KVM (Keyboard, Video, Mouse). Изделие может применяться в настольных рабочих станциях, а также в стоечных серверах. Новинка представляет собой альтернативу крошечному модулю NanoKVM, вышедшему летом нынешнего года. В основу NanoKVM-PCIe положен чип Sophgo SG2002, который объединяет два ядра C906 с архитектурой RISC-V (1000 и 700 МГц), одно ядро Arm Cortex-A53, а также контроллер 8051 с частотой от 25–300 МГц. Есть нейропроцессорный блок с производительностью до 1 TOPS (INT8) и 256 Мбайт памяти DDR3. Карта располагает слотом microSD, интерфейсом HDMI с поддержкой видео 1080p60, сетевым портом 10/100MbE RJ45 с опциональной поддержкой PoE, а также двумя разъёмами USB Type-C. Дополнительно в оснащение может быть включён адаптер Wi-Fi 6 с коннектором для антенны. Особенность NanoKVM-PCIe заключается в наличии небольшого информационного OLED-дисплея с диагональю 0,49″ и разрешением 64 × 32 точки: этот экран расположен на монтажной планке. Плата имеет низкопрофильное исполнение с габаритами 66 × 57 × 18 мм. Питание (0,2 A / 5 В) может подаваться через слот PCIe, порт USB Type-C или посредством PoE. Применяется прошивка с поддержкой управления UEFI/BIOS, эмулированными USB-мышью/клавиатурой и USB-накопителем, IPMI, WoL, Tailscale, WebSSH и пр. компания Sipeed принимает предварительные заказы на новинку по цене от $42 до $58 в зависимости от выбранных опций.

17.12.2024 [11:50], Сергей Карасёв

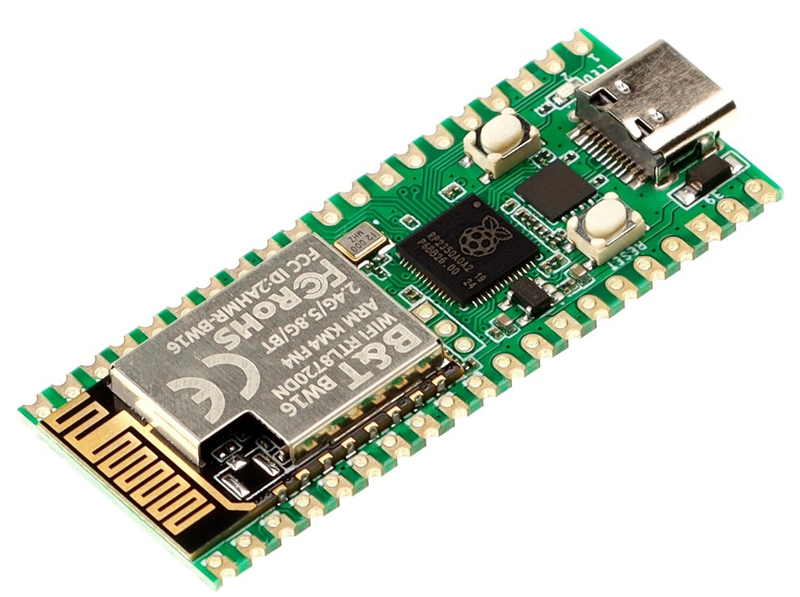

Вышла крошечная плата Pico W5 с контроллером Raspberry Pi RP2350, Wi-Fi 4 и Bluetooth 5.0По сообщению ресурса CNX Software, в продажу поступила микроплата Pico W5, построенная на контроллере Raspberry Pi RP2350. Изделие может стать альтернативой устройству Raspberry Pi Pico 2 W, которое дебютировало менее месяца назад. Чип RP2350 содержит по два ядра Arm Cortex-M33 и RISC-V Hazard3 с тактовой частотой 150 МГц. Однако использовать их одновременно нельзя: нужная пара ядер выбирается при инициализации платы. Объём встроенной памяти SRAM составляет 520 Кбайт. Реализована функция Secure Boot (только при использовании блока Arm). Новинка несёт на борту 8 Мбайт памяти QSPI Flash. В оснащение входят адаптеры Wi-Fi 4 802.11n (частотные диапазоны 2,4 и 5 ГГц) и Bluetooth 5.0 (LE) на основе модуля BW16 (контроллер Realtek RTL8720DN). Предусмотрен порт USB Type-C 1.1.

Источник изображения: CNX Software Крошечная плата Pico W5 располагает 26 контактами GPIO с поддержкой 2 × UART, 2 × SPI, 2 × I2C, 24 × PWM, 4 × ADC. Габариты составляют 51 × 21 мм, масса — 3 г. Питание (5 В) подаётся через коннектор USB Type-C. Диапазон рабочих температур простирается от -10 до +60 °C. Модель Pico W5 поддерживает разработку на базе Arduino и MicroPython. Приобрести новинку можно по ориентировочной цене $7. Столько же стоит оригинальная версия Raspberry Pi Pico 2 W, но это изделие поддерживает Wi-Fi 802.11n только в диапазоне 2,4 ГГц.

01.12.2024 [11:25], Сергей Карасёв

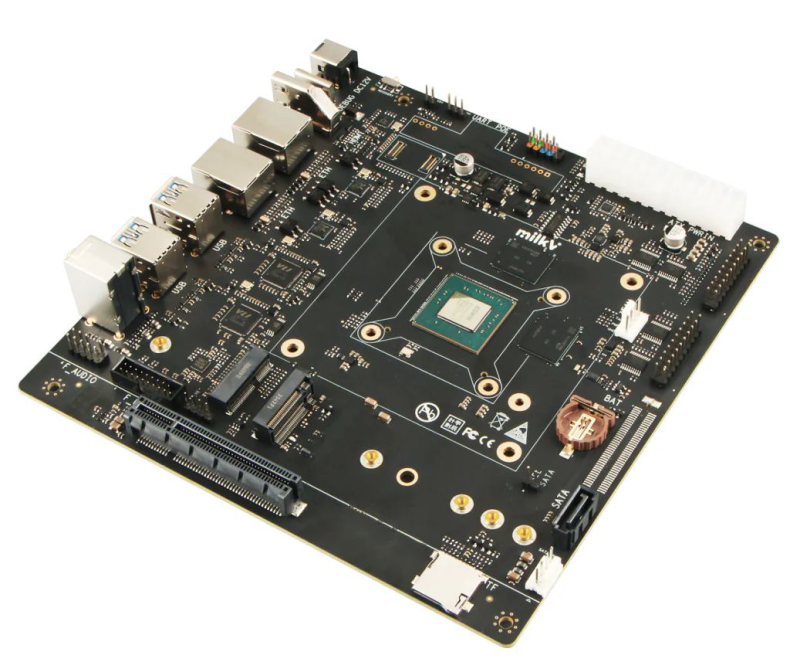

Плата Milk-V Megrez формата Mini-ITX с чипом RISC-V и NPU-модулем стоит $200В продажу поступила компактная плата Milk-V Megrez, предназначенная для построения систем на архитектуре RISC-V. Новинка ориентирована в первую очередь на разработчиков: говорится о поддержке таких фреймворков, как PyTorch, TensorFlow, PaddlePaddle, ONNX и пр. Изделие выполнено в форм-факторе Mini-ITX с размерами 170 × 170 мм. Применён процессор ESWIN EIC7700X: он содержит четыре ядра SiFive P550 (RV64CG) с тактовой частотой до 1,8 ГГц. Встроенный графический блок Imagination AXM-8-256 обладает поддержкой OpenGL ES 3.2, EGL 1.4, OpenCL 1.2/2.1 EP2, Vulkan 1.2. В состав чипа входит нейропроцессорный узел (NPU) с производительностью 19,95 TOPS в режиме INT8 и 9,975 TOPS в режиме INT16. Milk-V Megrez может нести на борту 8, 16 или 32 Гбайт оперативной памяти LPDDR5-6400 (впаяна на плату). Есть коннекторы M.2 для SSD с интерфейсом SATA-3 и eMMC для флеш-модуля, слот для карты microSD и порт SATA-3. Предусмотрен также слот PCIe х8 (PCIe 3.0 x4): возможна, в частности, установка ускорителя AMD 7900 XTX. В оснащение включены двухпортовый сетевой контроллер 1GbE и разъём M.2 E-Key для адаптера беспроводной связи. Для вывода изображения служит интерфейс HDMI 2.0. Заявлена возможность декодирования видеоматериалов H.265 8K@50р и кодирования H.265 up to 8K@25р. Доступны четыре порта USB 3.0 Type-A, два гнеза RJ-45 для сетевых кабелей, аудиовход и аудиовыход на 3,5 мм. Питание (12 В) может подаваться через DC-разъём. Цена платы варьируется от $200 до $270 в зависимости от объёма ОЗУ.

26.11.2024 [10:05], Сергей Карасёв

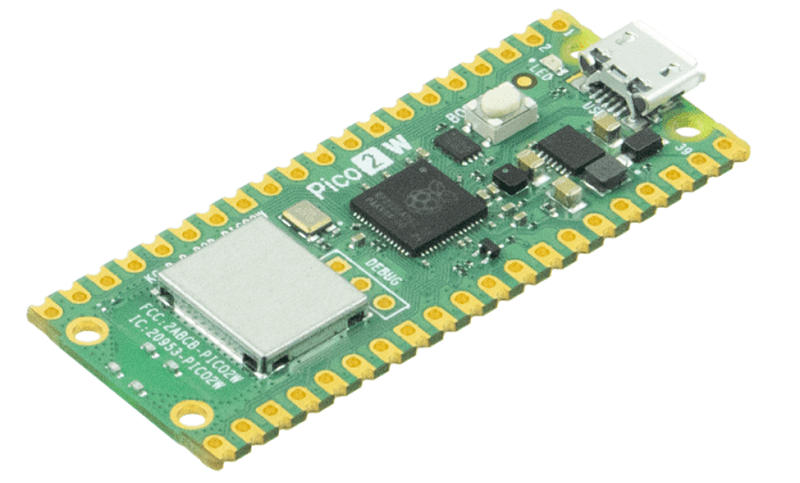

Вышла крошечная плата Raspberry Pi Pico 2 W за $7 с поддержкой Wi-Fi и Bluetooth 5.2Компания Raspberry Pi представила микроконтроллерную плату Pico 2 W — улучшенную версию Pico 2, дебютировавшей в августе нынешнего года. Новинка обзавелась поддержкой беспроводной связи Wi-Fi 802.11n (2,4 ГГц) и Bluetooth 5.2, которая отсутствует у оригинала. Анонсированная плата построена на микроконтроллере RP2350, объединяющем по два ядра Arm Cortex-M33 и RISC-V Hazard3 с тактовой частотой 150 МГц. Одна из двух пар ядер выбирается при инициализации устройства — использовать одновременно блоки Arm и RISC-V нельзя. В состав чипа входят 520 Кбайт памяти SRAM. Модель Pico 2 W несёт на борту 4 Мбайт флеш-памяти. Реализована поддержка 2 × UART, 2 × SPI, 2 × I2C, 24 × PWM, 3 × ADC. Кроме того, присутствует порт Micro-USB 1.1. Использовать плату можно при температурах от -20 до +85 °C. Диапазон входных напряжений — от 1,8 до 5,5 В.

Источник изображения: Raspberry Pi Новинка на программном и аппаратном уровнях совместима с Raspberry Pi Pico 1. Упомянута поддержка средств безопасности TrustZone для кластера Arm-ядер. Отмечается, что в целом архитектура безопасности RP2350, включая защищённую загрузочную область, подробно документирована и доступна всем пользователям без каких-либо ограничений. Программирование может осуществляться на C/C++ и Python. По заявлениям Raspberry Pi, плата Pico 2 W подходит как энтузиастам, так и профессиональным разработчикам, создающим решения на открытой платформе RISC-V. Новинку можно приобрести за $7, тогда как вариант без Wi-Fi и Bluetooth обойдётся в $5. Изделие предлагается по отдельности и в катушках по 480 модулей для промышленного использования.

19.11.2024 [11:47], Сергей Карасёв

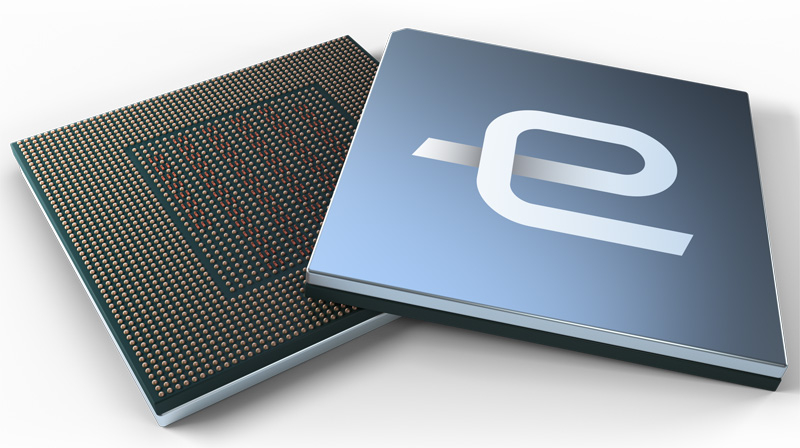

Esperanto и NEC займутся созданием HPC-решений на базе RISC-VСтартап Esperanto Technologies и корпорация NEC объявили о заключении соглашения о сотрудничестве в области НРС. Речь идёт о создании программных и аппаратных решений следующего поколения, использующих открытую архитектуру RISC-V. Напомним, Esperanto разрабатывает высокопроизводительные RISC-V-чипы для задач НРС и ИИ. Первым продуктом компании стало изделие ET-SoC-1, которое объединяет 1088 энергоэффективных ядер ET-Minion и четыре высокопроизводительных ядра ET-Maxion. Решение предназначено для инференса рекомендательных систем, в том числе на периферии. В августе 2023 года стало известно о подготовке чипа ET-SoC-2 с высокопроизводительными ядрами RISC-V с векторными расширениями. В рамках соглашения о сотрудничестве, как отмечается, будут объединены опыт и экспертизы NEC в области проектирования суперкомпьютеров и создания специализированного софта для HPC-задач с технологиями Esperanto в сфере высокопроизводительных энергоэффективных чипов на основе набора инструкций RISC-V. При этом упоминаются достижения NEC по направлению векторных процессоров: японская компания проектировала уникальные изделия SX-Aurora, но их разработка была остановлена в 2023 году.

Источник изображения: Esperanto «Используя глубокий опыт и экспертные знания NEC в области HPC, а также открытый набор инструкций RISC-V в сочетании с вычислительной технологией Esperanto, мы сможем разрабатывать масштабируемые и эффективные решения для ИИ и высокопроизводительных вычислений», — отметил Арт Свифт (Art Swift), президент и генеральный директор Esperanto.

25.10.2024 [13:24], Сергей Карасёв

От тостера до ЦОД: RISC-V International ратифицировала унифицированный профиль RVA23 для процессоров будущегоОрганизация RISC-V International объявила о ратификации профиля RVA23. Это значимое событие, которое, как ожидается, поможет открытой архитектуре RISC-V укрепить позиции по отношению к Arm и x86, избегая при этом потенциальных проблем, связанных с лицензированием. Профили RVA необходимы для обеспечения переносимости ПО между различными аппаратными реализациями. Таким образом, разработчики софта могут избежать привязки к конкретному поставщику аппаратных решений. Иными словами, одно и то же приложение сможет функционировать на любых устройствах, оснащённых процессорами с архитектурой RISC-V. Профиль RVA23 стандартизирует набор инструкций ISA (Instruction Set Architecture). Ключевой задачей является устранение фрагментации внутри экосистемы RISC-V. Отмечается, что в рамках ратификации профиль RVA23 прошёл длительный процесс разработки, рассмотрения и утверждения в многочисленных рабочих группах.

Источник изображения: pixabay.com RVA23 делает обязательными такие функции, как векторные операции, инструкции с плавающей запятой и атомарные инструкции, которые необходимы во многих сферах, включая НРС, машинное обучение и ИИ. В частности, векторные расширения ускоряют рабочие нагрузки с интенсивными математическими расчётами, включая криптографию, (де-)компрессию, обучение ИИ и пр. Важным компонентом RVA23 является поддержка гипервизоров. Это позволяет виртуализировать корпоративные рабочие нагрузки как на локальных серверах, так и в облаке. Таким образом, может быть ускорена разработка оборудования, ОС и прикладных программ для архитектуры RISC-V. Поддержка виртуализации также улучшит безопасность мобильных приложений путём разделения защищённых и незащищённых компонентов.

25.10.2024 [00:35], Игорь Осколков

NVIDIA за год отгрузила более 1 млрд RISC-V ядерВ рамках саммита RISC-V 2024 компания NVIDIA поделилась любопытной статистикой — за год в составе GPU и других ускорителей она отгрузила более 1 млрд ядер RISC-V собственной разработки, передаёт TechPowerUp. Они входят в состав GSP (GPU System Processor), который отвечает за управление GPU и иные служебные функции. В состав GSP входит от 10 до 40 ядер, в зависимости от сложности чипа, которым он управляет. Компания переключилась на разработку нового GSP на базе RISC-V в 2016 году. До этого более десяти лет NVIDIA использовала для GSP проприетарный процессор Falcon, возможностей и гибкости которого со временем стало не хватать. Вместо покупки и доработки готовых ядер от сторонних вендоров (Arm, MIPS, Synopsys ARC) или попыток улучшить Falcon, компания решила обратиться к открытой архитектуре RISC-V и к настоящему моменту разработала три типа ядер. Так, NV-RISCV32 представляет собой самое простое 32-бит ядро без внеочередного исполнения, работающее на частоте до 1,8 ГГц и имеющее производительность до 1,8 CoreMark/МГц. NV-RVV является NV-RISCV32 с 1024-бит векторными расширениями. А NV-RISCV64 — это уже более серьёзное 64-бит ядро с поддержкой внеочередного исполнения и SMP, частотой 2 ГГц и производительностью 5 CoreMark/МГц. Кроме того, NVIDIA разработала более 20 расширений ISA под специфические задачи. Впервые GSP на базе RISC-V появился в поколении Turing в 2018 году. Сейчас GSP отвечает за управление питанием и ресурсами ускорителя, безопасность, межчиповое взаимодействие, управление видеокодеками, вывод видео, работу с NVDLA и т.д. Google выбрала похожий путь — в её ИИ-ускорителях TPU используются ядра SiFive. Впрочем, сейчас есть уже и «большие» ИИ-ускорители, построенные исключительно на ядрах RISC-V: Meta✴ MTIA первого и второго поколений, InspireSemi Thunderbird, Tenstorrent Wormhole и Grayskull, а также Esperanto ET-SoC-1 и ET-SoC-2.

22.10.2024 [10:50], Сергей Карасёв

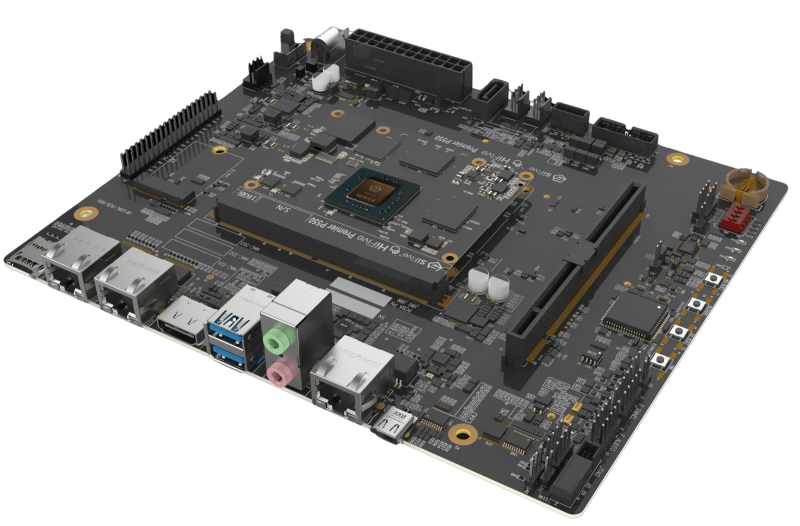

Плата HiFive Premier P550 формата mini-DTX оснащена чипом RISC-V с ИИ-ускорителемКомпания SiFive анонсировала плату HiFive Premier P550, в основу которой положен вычислительный модуль (SoM) с процессором ESWIN EIC7700X. Новинка, рассчитанная прежде всего на разработчиков, выполнена в форм-факторе mini-DTX с размерами 203 × 170 мм. Чип EIC7700X объединяет четыре ядра SiFive Performance P550 RV64GC с открытой архитектурой RISC-V: их базовая частота составляет 1,4 ГГц (повышается до 1,8 ГГц). Встроенный графический блок Imagination AXM-8-256 3D GPU обладает поддержкой OpenGL-ES 3.2, EGL 1.4, OpenCL 1.2/2.1 EP2, Vulkan 1.2, Android NN HAL. Для ускорения ИИ-операций служит нейропроцессорный узел (NPU) с производительностью 19,95 TOPS в режиме INT8 и 9,975 TOPS в режиме INT16. Вычислительный модуль несёт на борту 16 или 32 Гбайт памяти LPDDR5-6400 и чип eMMC 5.1 вместимостью 128 Гбайт. SoM устанавливается на интерфейсную плату с набором разъёмов. В их число входят порт SATA-3 для накопителя, слот для карты microSD, два сетевых порта 1GbE RJ45 и дополнительный порт RJ45 для удалённого управления, два разъёма USB 3.2 Gen1 Type-A (USB 3.0) + колодка для ещё двух таких же портов и коннектор USB Type-E, аудиогнёзда 3,5 мм, интерфейс HDMI 2.0 и порт USB Type-C (USB 2.0, UART/JTAG). Кроме того, есть коннектор M.2 Key E для комбинированного адаптера Wi-Fi/Bluetooth, слот PCIe 3.0 x16 (работает в режиме х4), 40-контактная колодка ввода/вывода (1 × I2C, 1 × QSPI, 1 × UART, 16 × GPIO). Новинка справляется с декодированием видеоматериалов H.265 8K со скоростью до 50 к/с. Предусмотрены разъёмы для подключения трёх вентиляторов охлаждения. Говорится о совместимости с Ubuntu 24.04, Freedom U-SDK, OpenSBI и U-Boot. Приобрести решение можно по ориентировочной цене $600 в версии с 16 Гбайт ОЗУ.

04.10.2024 [14:35], Сергей Карасёв

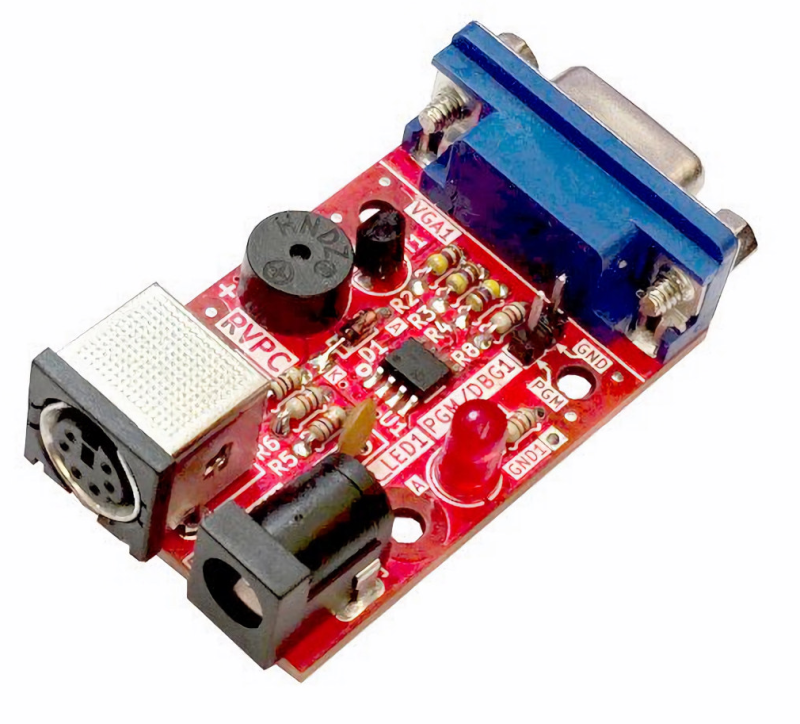

Микрокомпьютер с микроконтроллером по микроцене: Olimex RVPC за €1 получил чип RISC-V, порт PS/2 и видеовыход D-SubКомпания Olimex анонсировала одноплатную систему RVPC, оснащённую микроконтроллером с открытой архитектурой RISC-V. Изделие будет поставляться в виде комплекта для самостоятельной пайки, что позволит использовать его в том числе в образовательных целях. Сам производитель относит новинку к ретрокомпьютерам. Задействован 32-битный чип WCH CH32V003 RISC-V2A с частотой 48 МГц. Есть 2 Кбайт памяти SRAM и 16 Кбайт флеш-памяти. Предусмотрены аналоговый интерфейс D-Sub для подключения монитора (три линии GPIO для Vsync, HSync и RGB), а также коннектор PS/2 для клавиатуры (две линии GPIO). Новинка имеет размеры 50 × 30 мм. Питание (5 В) подаётся через отдельный разъём. Программирование микроконтроллера CH32V003 может осуществляться через вспомогательную плату ESP32-S2-DevKit-LiPo-USB. Среди прочего упомянуты зуммер и светодиодный индикатор состояния. Olimex предоставляет несколько примеров программного кода на языке C для использования интерфейса D-Sub, демонстрационную игру Tetris, эмулятор терминала (RVMON), который предварительно загружен во флеш-память, и пр. Цена Olimex RVPC составляет всего €1. При этом плата ESP32-S2-DevKit-LiPo-USB обойдётся ещё примерно в €8. За совместимый адаптер питания компания просит около €4.

03.10.2024 [10:10], Сергей Карасёв

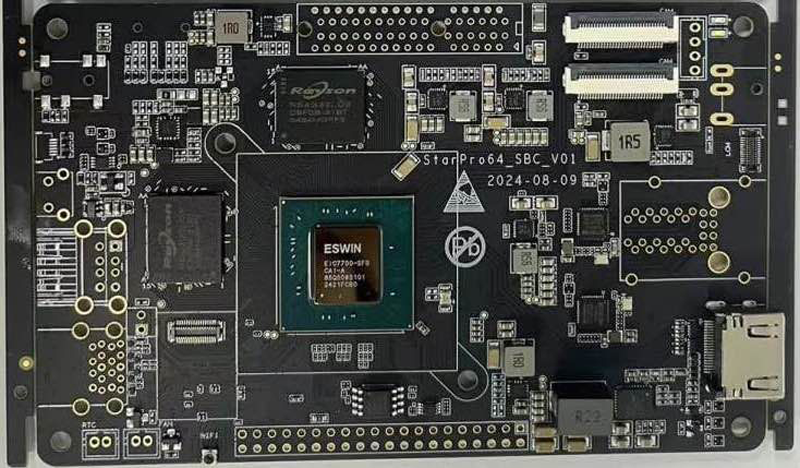

Одноплатный компьютер StarPro64 оснащён процессором RISC-V с ИИ-ускорителем и до 32 Гбайт LPDDR5Команда Pine64 разработала одноплатный компьютер StarPro64, оснащённый процессором с открытой архитектурой RISC-V. Поставки новинки, ориентированной на разработчиков, будут организованы в ближайшее время. Устройство несёт на борту чип ESWIN EIC7700X с четырьмя ядрами SiFive Performance P550 RV64GC RISC-V с тактовой частотой до 1,8 ГГц. Утверждается, что по производительности эти ядра сопоставимы с Cortex-A75. Встроенный блок 3D GPU обеспечивает возможность декодирования видео H.265 в формате 8K со скоростью до 50 кадров в секунду. Упомянута поддержка OpenGL-ES 3.2, EGL 1.4, OpenCL 1.2/2.1 EP2, Vulkan 1.2, Android NN HAL. Кроме того, имеется нейропроцессорный узел с производительностью 19,95 TOPS (INT8) для ускорения ИИ-операций.

Источник изображения: Pine64 Одноплатный компьютер будет предлагаться в модификациях с 8, 16 и 32 Гбайт оперативной памяти LPDDR5. В оснащение входят слот для карты microSD и разъём для флеш-накопителя eMMC. Среди доступных интерфейсов упомянуты PCIe x4, USB 3.0 и USB 2.0. Процессор ESWIN EIC7700X также обеспечивает поддержку HDMI 2.0, MIPI-DSI TX (4 линии), LVDS/Sub-LVDS/HiSPi (4 линии), 12 × I2C, 3 × I2S и пр. Новинка имеет размеры 133 × 80 × 19 мм. Есть двухпортовый сетевой контроллер Ethernet, адаптеры Wi-Fi и Bluetooth, колодка GPIO. Дополнительно может быть установлен радиатор охлаждения. При необходимости можно подключить дисплей PinePhone Pro LCD или сенсорную панель. |

|