Материалы по тегу: sifive

|

09.09.2025 [17:00], Владимир Мироненко

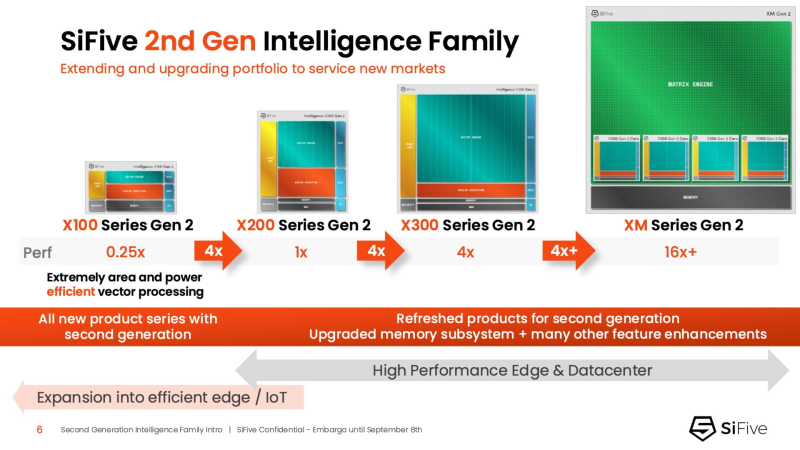

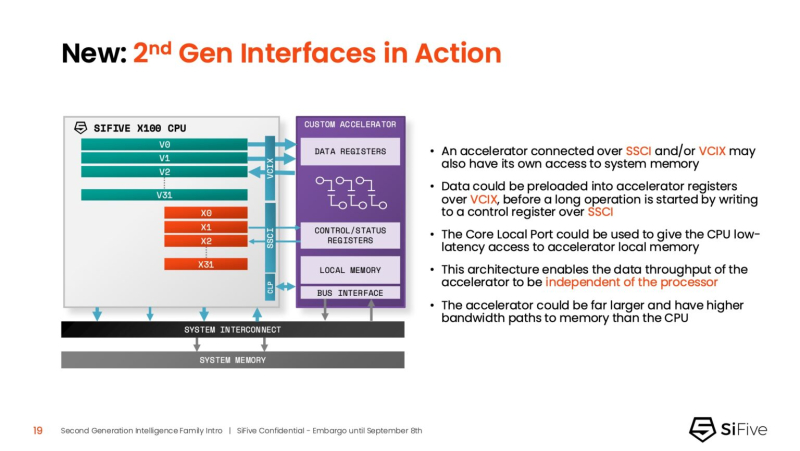

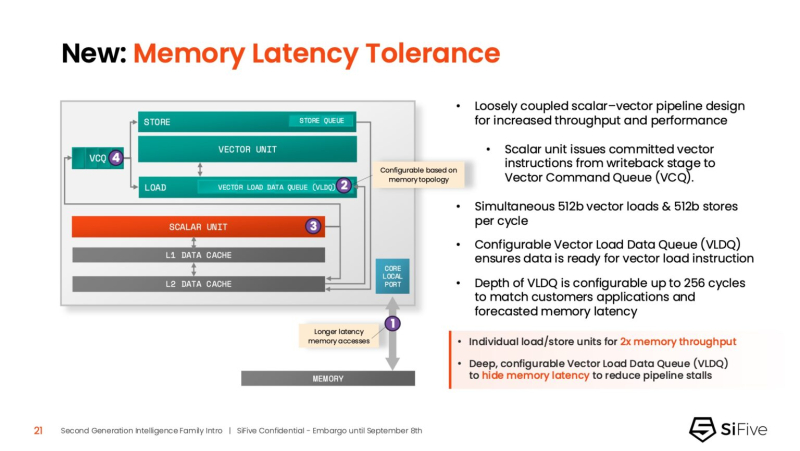

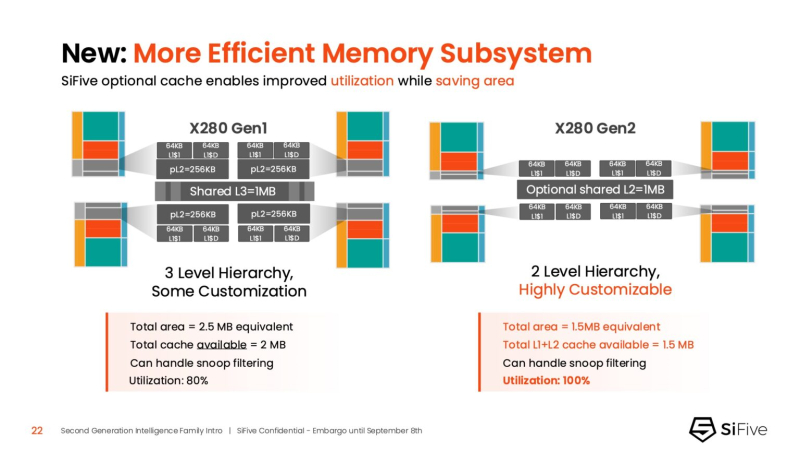

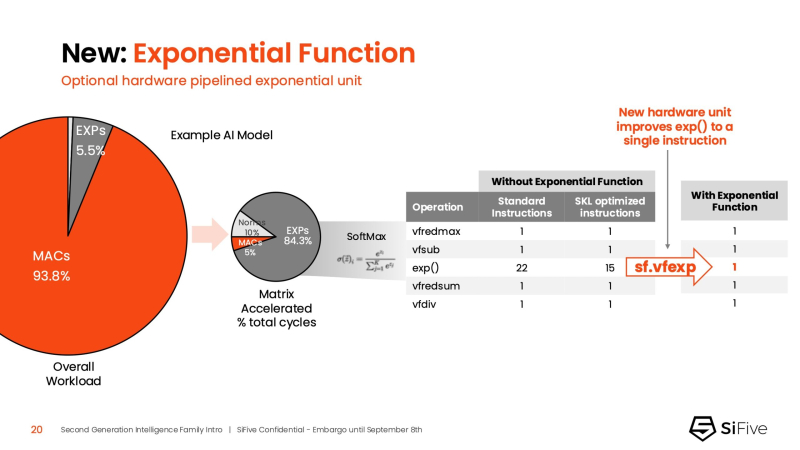

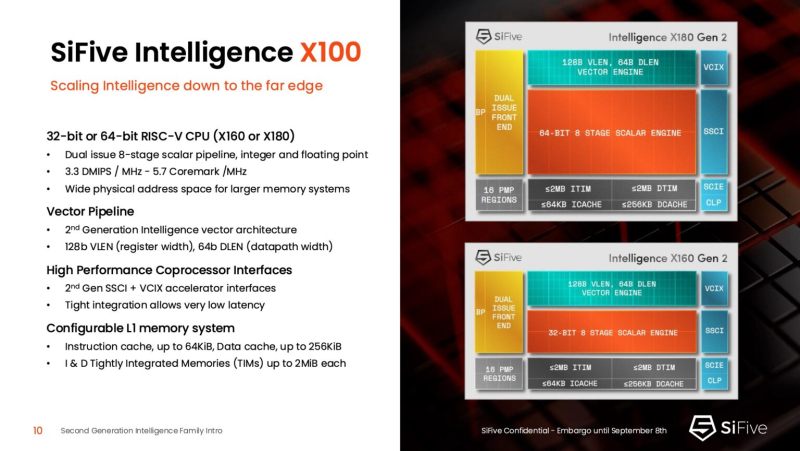

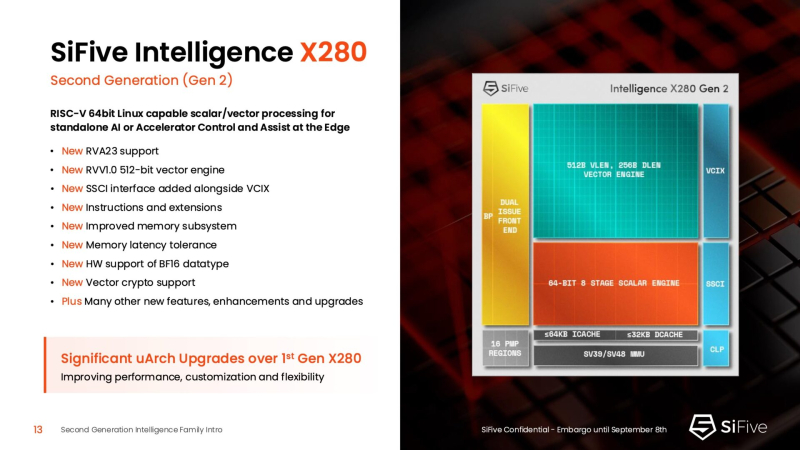

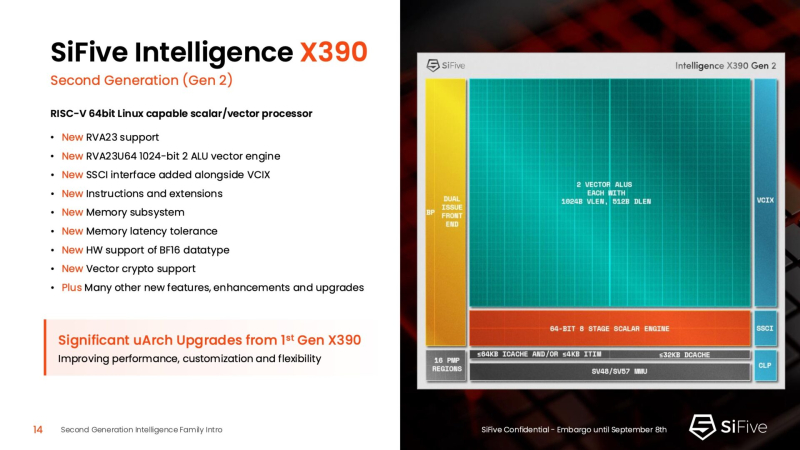

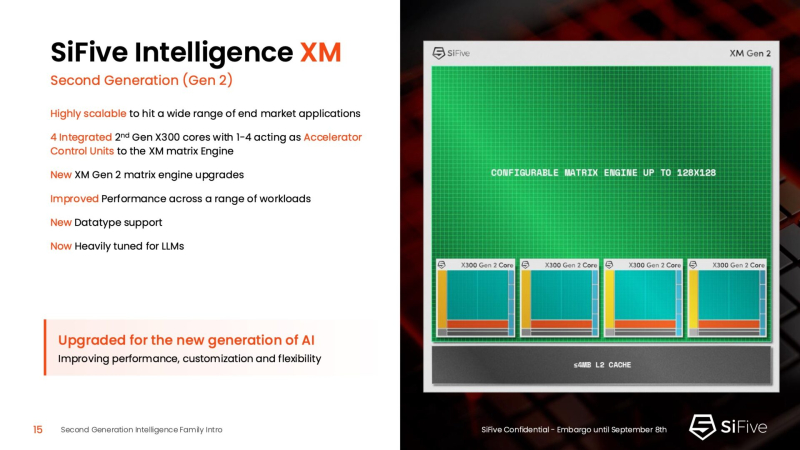

Быстрее и «умнее»: SiFive представила второе поколени RISC-V-ядер IntelligentSiFive представила семейство ядер Intelligent второго поколения с архитектурой RISC-V, включающее новые ядра X160 Gen 2 и X180 Gen 2, а также обновлённые решения X280 Gen 2, X390 Gen 2 и XM Gen 2. Новые решения разработаны для расширения возможностей скалярной, векторной и, в случае серии XM, матричной обработки данных, адаптированных для современных задач в сфере ИИ. Как отметил ресурс EE Times, анонсируя новую линейку продуктов, SiFive стремится воспользоваться быстрорастущим спросом на решения для обработки ИИ-нагрузок, который, по прогнозам Deloitte, вырастет как минимум на 20 % во всех технологических средах, включая впечатляющий скачок на 78 % в сфере периферийных вычислений с использованием ИИ. Ядра SiFive второго поколения позволяют решать критически важные задачи в области внедрения ИИ, в частности, в области управления памятью и ускорения нелинейных функций. Ключевым нововведением в процессорах серии X является их способность функционировать в качестве блока управления ускорителем (ACU). Это позволяет ядрам SiFive обеспечивать основные функции управления и поддержки для ускорителя заказчика через интерфейсы SiFive Scalar Coprocessor Interface (SSCI) и Vector Coprocessor Interface eXtension (VCIX). Данная архитектура позволяет заказчикам сосредоточиться на инновациях в обработке данных на уровне платформы, оптимизируя программный стек. Джон Симпсон (John Simpson), главный архитектор SiFive, сообщил ресурсу EE Times, что интеллектуальные ядра SiFive обеспечивают гибкость, сокращают трафик системной шины за счёт локальной обработки на чипе ускорителя и обеспечивают более тесную связь для задач пред- и постобработки. Он рассказал, что SiFive представила два важных усовершенствования в архитектуре, которые напрямую устраняют узкие места производительности: устойчивость к задержкам памяти и более эффективную подсистему памяти. Функцию Memory Latency Tolerance позволяет снизить задержку загрузки. Симпсон рассказал, что блок скалярных вычислений, обрабатывающий все инструкции, отправляет векторные инструкции в очередь векторных команд (VCQ). При обнаружении такого инструкции одновременно отправляется запрос в подсистему памяти (кеш L2 или выше). Ранняя отправка запросов, отделённая от исполнения, позволяет быстрее получить ответ от памяти и поместить его в переупорядочиваемую настраиваемую очередь загрузки векторных данных (VLDQ). Это гарантирует готовность данных к моменту, когда инструкция в конечном итоге покинет VCQ, что приводит к «загрузке вектора в течение одного цикла». Симпсон подчеркнул конкурентное преимущество решения, отметив: «Xeon, представленный на Hot Chips, может обслуживать 128 невыполненных запросов, и это топовый показатель для Xeon, а в нашем четырёхъядерном процессоре этот показатель составляет 1024». Эта «прекрасная технология» обеспечивает непрерывную обработку данных, эффективно предотвращая простои конвейера. Более эффективная подсистема памяти, которая представляет собой ещё одно существенное обновление, основана на переходе от инклюзивной к неинклюзивной иерархии кешей. В инклюзивной системе кеширования предыдущего поколения данные из общего кеша L3 реплицировались в частные кеши L1/L2, что компания посчитала неэффективным расходом «кремния». Конструкция ядер второго поколения исключает копирование, что, по словам Симпсона, даёт «в 1,5 раза большую производительность по сравнению с первым поколением» при меньшей занимаемой площади на кристалле. SiFive также интегрировала новый аппаратный конвейерный экспоненциальный блок. В то время как MAC-операции доминируют в рабочих ИИ-нагрузках, возведение в степень становится следующим серьёзным узким местом. Например, в BERT LLM, ускоренных матричным движком, операции softmax, включающие возведение в степень, занимают более 50 % оставшихся циклов. Программными оптимизациями SiFive сократила выполнение функции возведения в степень с 22 до 15 циклов, а новый аппаратный блок сокращает её до одной инструкции, уменьшая общее время выполнения функции до пяти циклов. Программный стек для семейства Intelligence второго поколения поддерживает масштабируемость. В серии XM среда выполнения машинного обучения уже распределяет рабочие нагрузки между несколькими кластерами XM на одном кристалле. Впрочем, пока масштабирование за пределы одного кристалла требует дальнейшей разработки библиотеки межпроцессорного взаимодействия (IPC). Флагманские решения X160 Gen 2 и X180 Gen 2 могут быть настроены для работы под управлением операционной системы реального времени, пишет SiliconANGLE. 32-бит IP-ядро Intelligence X160 разработано для оптимизации энергоэффективности и приложений с жесткими ограничениями по площади кристалла, в то время как 64-бит IP-ядро Intelligence X180 обеспечивает более высокую производительность и лучшую интеграцию с более крупными подсистемами памяти, сообщил ресурс CNX-Software. X160 поставляется с кеш-памятью объёмом до 200 КиБ и памятью объёмом 2 МиБ. Помимо промышленного оборудования, ядро может найти применение в потребительских устройствах, таких как фитнес-трекеры. Кроме того, X160 можно установить в системах с несколькими ИИ-ускорителями для управления чипами и предотвращения изменения прошивки. Благодаря двум встроенным кешам общей ёмкостью более 4 МиБ ядро позволяет работать с большим объёмом данных. По данным SiFive, X160 подходит для обучения ИИ-моделей и использования в оборудовании ЦОД. В свою очередь, ядро X280 ориентировано на потребительские устройства, такие как гарнитуры дополненной реальности, а X390 также может использоваться в автомобилях и инфраструктурных системах. Последнее ядро выполняет векторную обработку в четыре раза быстрее, чем X280. Все пять продуктов Intelligence Gen 2 уже доступны для лицензирования, а появление первых чипов на их основе ожидается во II квартале 2026 года. SiFive сообщила, что два ведущих американских производителя полупроводников лицензировали новую серию X100 ещё до её публичного анонса. Они используют IP-ядро X100 в двух различных сценариях: одна компания задействует сочетание скалярного векторного ядра SiFive с матричным движком, выступающим в качестве блока управления ускорителем, а вторая использует векторный движок в качестве автономного ИИ-ускорителя.

22.10.2024 [10:50], Сергей Карасёв

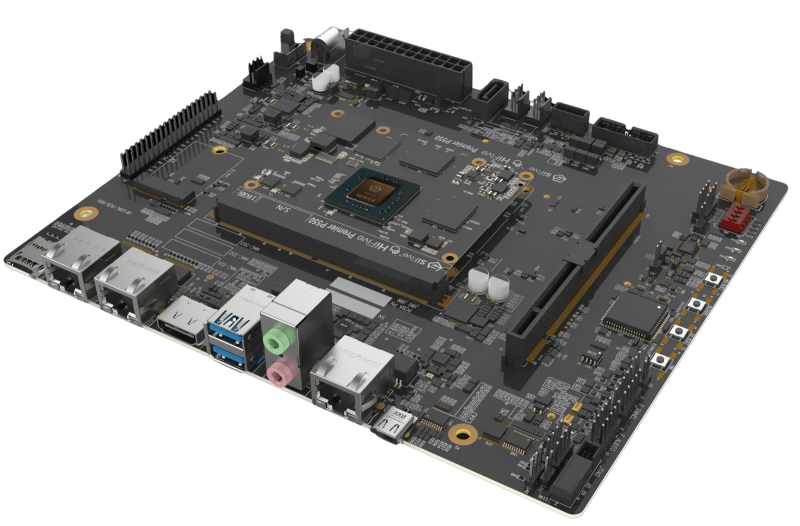

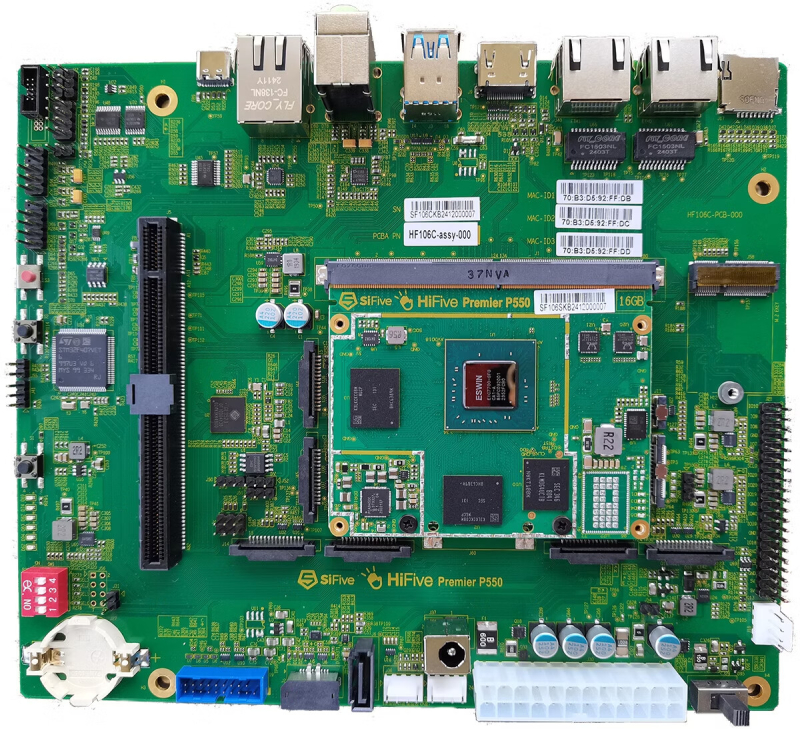

Плата HiFive Premier P550 формата mini-DTX оснащена чипом RISC-V с ИИ-ускорителемКомпания SiFive анонсировала плату HiFive Premier P550, в основу которой положен вычислительный модуль (SoM) с процессором ESWIN EIC7700X. Новинка, рассчитанная прежде всего на разработчиков, выполнена в форм-факторе mini-DTX с размерами 203 × 170 мм. Чип EIC7700X объединяет четыре ядра SiFive Performance P550 RV64GC с открытой архитектурой RISC-V: их базовая частота составляет 1,4 ГГц (повышается до 1,8 ГГц). Встроенный графический блок Imagination AXM-8-256 3D GPU обладает поддержкой OpenGL-ES 3.2, EGL 1.4, OpenCL 1.2/2.1 EP2, Vulkan 1.2, Android NN HAL. Для ускорения ИИ-операций служит нейропроцессорный узел (NPU) с производительностью 19,95 TOPS в режиме INT8 и 9,975 TOPS в режиме INT16. Вычислительный модуль несёт на борту 16 или 32 Гбайт памяти LPDDR5-6400 и чип eMMC 5.1 вместимостью 128 Гбайт. SoM устанавливается на интерфейсную плату с набором разъёмов. В их число входят порт SATA-3 для накопителя, слот для карты microSD, два сетевых порта 1GbE RJ45 и дополнительный порт RJ45 для удалённого управления, два разъёма USB 3.2 Gen1 Type-A (USB 3.0) + колодка для ещё двух таких же портов и коннектор USB Type-E, аудиогнёзда 3,5 мм, интерфейс HDMI 2.0 и порт USB Type-C (USB 2.0, UART/JTAG). Кроме того, есть коннектор M.2 Key E для комбинированного адаптера Wi-Fi/Bluetooth, слот PCIe 3.0 x16 (работает в режиме х4), 40-контактная колодка ввода/вывода (1 × I2C, 1 × QSPI, 1 × UART, 16 × GPIO). Новинка справляется с декодированием видеоматериалов H.265 8K со скоростью до 50 к/с. Предусмотрены разъёмы для подключения трёх вентиляторов охлаждения. Говорится о совместимости с Ubuntu 24.04, Freedom U-SDK, OpenSBI и U-Boot. Приобрести решение можно по ориентировочной цене $600 в версии с 16 Гбайт ОЗУ.

20.09.2024 [21:27], Алексей Степин

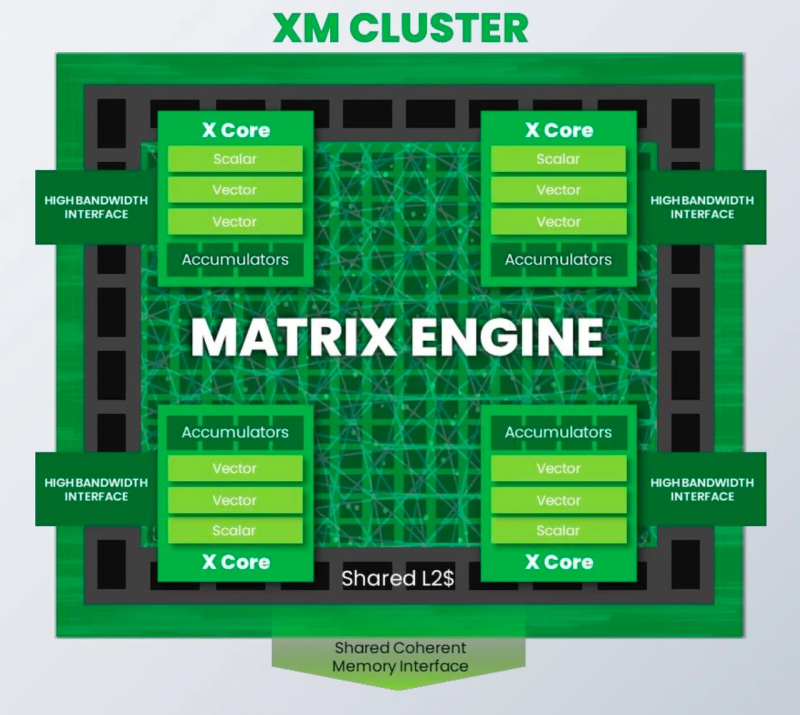

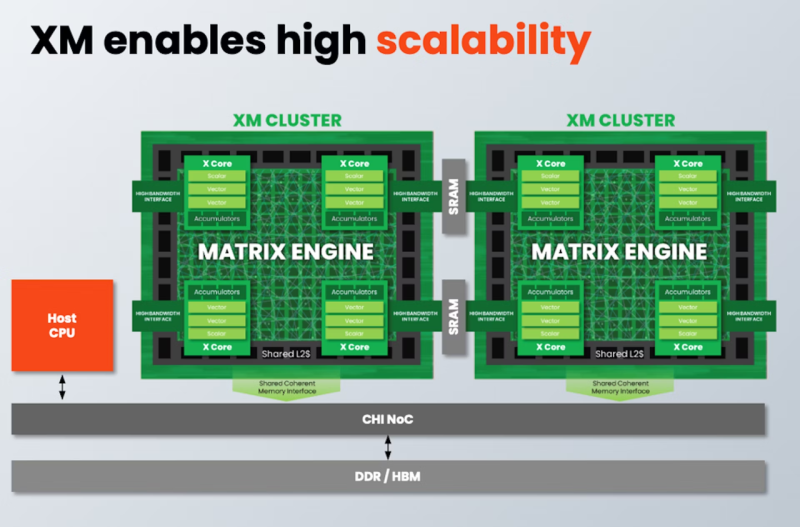

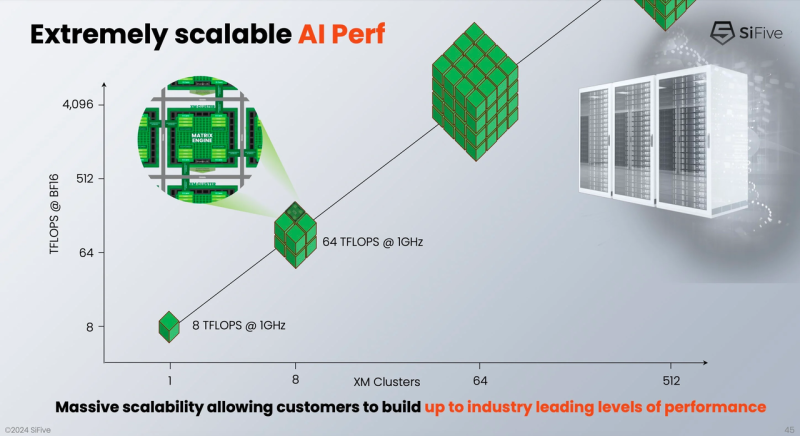

От IoT до ЦОД: SiFive представила экономичные ИИ-ядра Intelligence XMРазработчик SiFive, известный своими процессорными ядрами с архитектурой RISC-V, решил подключиться к буму систем ИИ, анонсировав кластеры Intelligence XM — первые в индустрии RISC-V решения, оснащённые масштабируемым движком матричных вычислений для обработки ИИ-нагрузок. Как отмечает SiFive, новый дизайн должен помочь разработчикам чипов на базе RISC-V в создании кастомных ИИ-систем, в том числе для автономного транспорта, робототехники, БПЛА, IoT, периферийных вычислений и т.п., где роль таких нагрузок в последнее время серьёзно выросла, а требование к энергоэффективности никуда не делись. Но при желании можно создать и серверные ускорители, говорит компания. Каждый матричный блок в составе одного XM-кластера дополнен четырьмя ядрами X Core, каждое из которых имеет в своём составе два блока векторных вычислений и один блок скалярных вычислений. Все вместе они делят общий L2-кеш. XM-кластер располагает шиной с пропускной способностью 1 Тбайт/с и поддерживает подключение к памяти двух типов — когерентное через общую шину CHI, к которой подключается и внешняя память DDR/HBM, или высокоскоростной порт для SRAM. Производительность одного XM-кластера 8 Тфлопс в режиме BF16 и 16 Топс в режиме INT8 на каждый ГГц частоты. Тип хост-ядра не важен, это может быть RISC-V, Arm или даже x86. Впрочем, хост-ядра могут отсутствовать вовсе. Ожидается, что чипы на базе XM в среднем будут иметь от четырёх до восьми кластеров, что даст им до 8 Тбайт/с пропускной способности памяти и до 64 Тфлопс производительности в режиме BF16, и это лишь на частоте 1 ГГц при малом уровне энергопотребления. Но возможно и масштабирование до 512 XM-блоков, что даст уже 4 Пфлопс BF16. У NVIDIA Blackwell, например, в том же режиме производительность составляет 5 Пфлопс. В целях дальнейшей популяризации архитектуры RISC-V компания также планирует сделать открытой (open source) референсную имплементацию SiFive Kernel Library (SKL). SKL включает оптимизированную для RISC-V ядер SiFive реализацю различных востребованных алгоритмов, в том числе для работы с нейронными сетями, обработки сигналов, линейной алгебры и т.д. Дела у SiFive идут, судя по всему, неплохо, и, как отметил глава компании Патрик Литтл (Patrick Little), новые дизайны ядер помогут ей сохранить темпы роста и не отстать от эволюции ИИ, оставаясь в то же время поставщиком уникальных процессорных решений с открытой архитектурой. На данный момент решения SiFive уже поставляет свои решения таким гигантам, как Alphabet, Amazon, Apple, Meta✴, Microsoft, NVIDIA и Tesla.

15.08.2024 [09:36], Алексей Степин

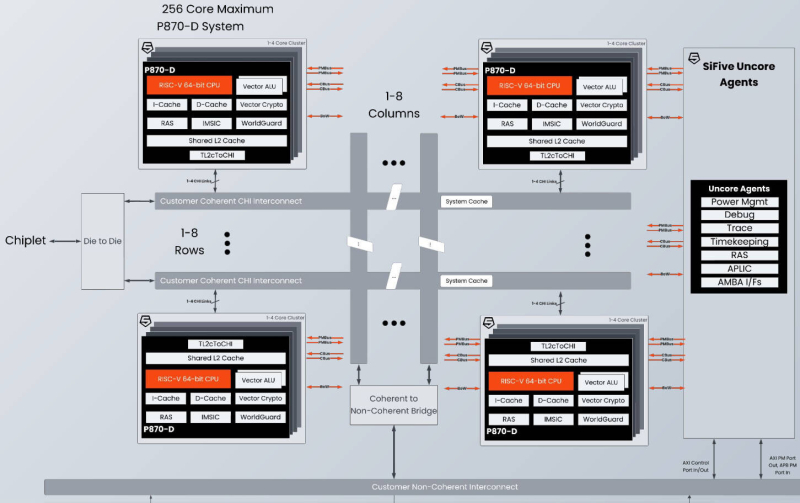

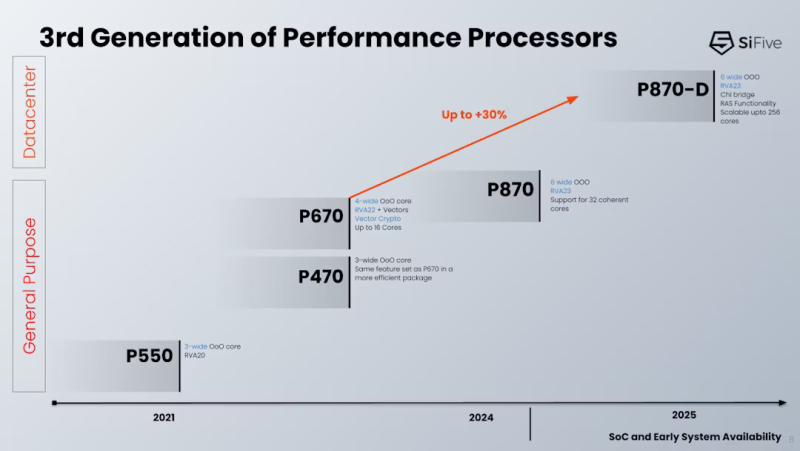

256 × RISC-V: SiFive представила высокопроизводительные ядра P870-D для серверов и СХДОткрытая архитектура RISC-V, которая, как многие надеются, станет конкурентом Arm не только в компактных и экономичных устройствах, но и в серверных системах, продолжает развиваться. Один из ведущих разработчиков в этой сфере, компания SiFive, анонсировала новое ядро P870-D. Как следует из системы обозначений, принятой SiFive, это высокопроизводительное (Performance) ядро, а суффикс D означает Datacenter. Новинка предназначена для серверных процессоров с количеством ядер до 256. Дизайн P870-D нельзя назвать полностью новым, поскольку он основан на ядре P870, анонсированном в конце 2023 года. Данное решение предназначалось для создания процессоров с числом ядер до 32 и включало в себя два 128-бит векторных блока, при этом каждые четыре ядра группировались в кластер, использовавший разделяемый кеш L2. P870-D сохранило черты предшественника. Это 64-бит ядро с поддержкой внеочередного исполнения инструкций и шириной декодера 6. В нём реализована поддержка набора инструкций RVA 23, Vector 1.0 и Vector Crypto. Появилась поддержка функций обеспечения повышенной надёжности RAS (Reliability, availability and serviceability). Контроль чётности присутствует уже на уровне регистровых файлов, а на всех уровнях подсистемы кешей имеется коррекция ошибок SECDED ECC. Но это не всё, в P870D есть поддержка AMBA CHI (4 порта). Это нововведение позволило SiFive существенно улучшить масштабирование — P870-D может служить основой для процессоров с числом ядер до 256, включая гетерогенные, в том числе возможны многочиповые дизайны и варианты с поддержкой CXL. Сами ядра по-прежнему группируются в кластеры по четыре, а CHI-подключение может обеспечиваться как встроенным мостом, так и внешним чиплетом. Также в состав P870-D входит распределённый масштабируемый блок IOMMU, платформа безопасности WorldGuard и uncore-агент, ответственный за питание, отладку, трассировку и т.д. Есть и контроллер прерываний Advanced Interrupt Architecture (AIA) с поддержкой Message Signal Interrupts (MSI) и виртуализации. В настоящее время это самое мощное ядро в арсенале SiFive, основными его конкурентами названы Arm Cortex-X2 и AMD Zen 4c. Однако перекоса в сторону исключительно производительности у P870-D нет. Поскольку данный дизайн ориентирован на современные высокоплотные ЦОД и платформы периферийных вычислений, разработчики уделили серьёзное внимание вопросам энергопотребления и тепловыделения. Впрочем, точных данных по этим параметрам пока приведено не было. Компания активно сотрудничает с партнерами по экосистеме RISC-V. Так, уже заключено соглашение с Arteris, которая выпустит референсные платформы валидации на базе P870-D и X280 с интегрированной поддержкой Arteris Network-on-Chip (NoC), что должно упростить дальнейшую разработку сложных гетерогенных чипов с функциями ИИ (за счёт блоков SiFive Intelligence) и ускорить вывод на рынок решений на базе таких чипов. Образцы чипов на базе SiFive P870-D уже поставляются ведущим партнёрам компании, а начало массового производства намечено на конец текущего 2024 года. Зарубежные аналитики полагают, что за энергоэффективными платформами на базе открытых стандартов большое будущее. К 2030 году решения, подобные SiFive P870-D, как ожидается, займут более 40 % всего рынка серверных процессоров.

17.07.2024 [13:16], Сергей Карасёв

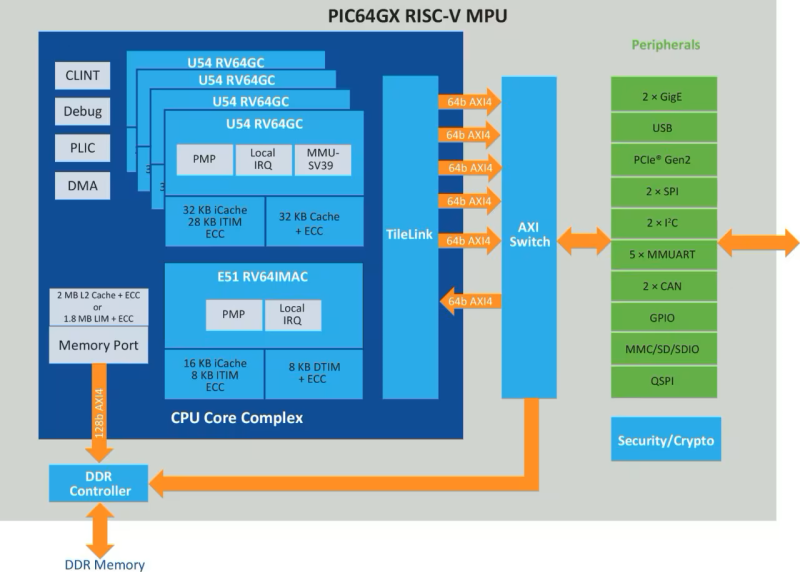

Microchip представила свои первые 64-бит чипы PIC64GX на архитектуре RISC-VКомпания Microchip Technology анонсировала изделия PIC64GX — своё первое семейство 64-бит чипов, выполненных на открытой архитектуре RISC-V. Среди ключевых сфер применения названы устройства для промышленного, автомобильного, коммуникационного, аэрокосмического и оборонного сегментов, а также для Интернета вещей. Первым представителем нового семейства стал чип PIC64GX1000. Он содержит четыре 64-битных ядра SiFive U54 (RV64GC) без внеочередного исполнения инструкций, но с блоком управления памятью (MMU). Тактовая частота достигает 625 МГц. Кроме того, присутствует вспомогательное ядро SiFive E51 RISC-V (RV64IMAC) с той же частотой, отвечающее за функции мониторинга. Чип может работать как в режиме SMP, так и AMP. Заявленный уровень производительности составляет порядка 5 тыс. DMIPS. Реализована подсистема кеша L1 с функциями коррекции ошибок Single-Error Correct, Double-Error Detect (SECDED). Объём кеша L2 с поддержкой SECDED составляет 2 Мбайт (SRAM). Все кеши можно переконфигурировать под свои нужды. Также есть 128 Кбайт энергонезависимой памяти для загрузчика и 56 Кбайт защищённой памяти для хранения пользовательских данных и ключей. Имеется встроенный 36-бит контроллер памяти (LP)DDR4-1333 (SECDED) с поддержкой до 32 Гбит на DDR-интерфейс. Реализована поддержка интерфейсов MMC 5.1, SD, SDIO, HDMI 1.4, MIPI CSI-2 (две линии), 2 × 1GbE, USB 2.0 OTG, PCIe 2.2 x4 (версия FCV) или x1 (модификация FCS), 2 × SPI, 5 × UART, 2 × I2C, 32 × GPIO, 2 × CAN. Средства обеспечения безопасности включают AES/SHA (256 бит), TRNG, HMAC, RSA, ECDSA. Доступны варианты упаковки FCSG325 (11 × 11 × 0,5 мм) c 200 контактами и FCVG484 (19 × 19 × 0,8 мм) с 244 контактами. Будут предлагаться коммерческая и индустриальная модификации: в первом случае диапазон рабочих температур простирается от 0 до +100 °C, во втором — от -40 до +100 °C.

27.06.2024 [11:04], Сергей Карасёв

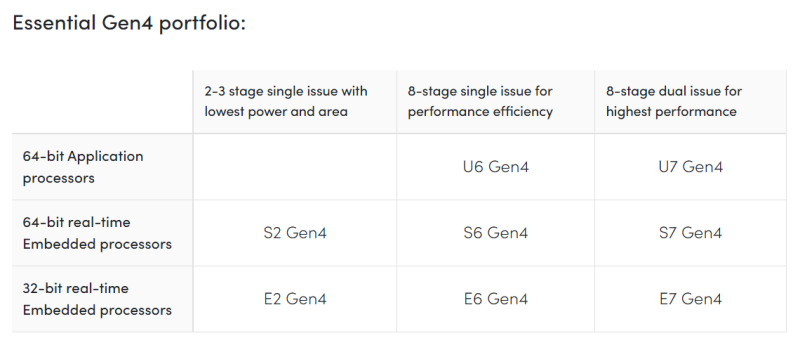

SiFive анонсировала новое семейство процессоров RISC-V для встраиваемых устройствКомпания SiFive, разработчик процессоров на архитектуре RISC-V, представила решения семейства Essential Gen4 для различных встраиваемых устройств. В серию вошли восемь модификаций базовых ядер RISC-V, которые могут применяться в таком оборудовании, как камеры наблюдения, решения FPGA, накопители на основе флеш-памяти, носимые гаджеты и пр. В частности, анонсированы 64-бит решения U6 и U7 для процессоров приложений, 64-бит ядра реального времени S2, S6 и S7 для встраиваемых систем, а также 32-бит ядра реального времени E2, E6 и E7. Для новинок заявлено снижение энергопотребления в рабочем режиме до 40 % по сравнению с ядрами RISC-V предыдущего поколения. Говорится об улучшенном кеше L2 и расширенном кеше L1. Разработчикам предоставляются гибкие возможности в плане конфигурирования устройств: тип CPU, различные варианты интегрированной памяти, выбор периферийных компонентов и портов. Кроме того, упомянуты развитые средства управления питанием и обеспечения безопасности. Ядра SiFive Essential Gen4 могут использоваться со встраиваемыми ОС Linux и FreeRTOS. Заявлена интеграция с IDE Eclipse. В целом, изделия четвёртого поколения обеспечивают более высокую производительность, повышенную энергоэффективность и более гибкие возможности в плане использования интерфейсов. При этом полные технические характеристики новинок компания не раскрывает. Отмечается также, что на сегодняшний день по всему миру реализовано более 2 млрд чипов с ядрами SiFive RISC-V для встраиваемых устройств. Данный рынок продолжает активно развиваться, что говорит о росте популярности открытой архитектуры RISC-V.

09.04.2024 [12:57], Сергей Карасёв

SiFive представила RISC-V платформу для разработчиков HiFive Premier P550Компания SiFive представила платформу для разработчиков HiFive Premier P550 на архитектуре RISC-V. Новинка подходит для проектов, связанных с машинным зрением, видеоанализом, ИИ и пр. В основу решения положена «система на чипе» Eswin EIC7700 SoC с четырьмя вычислительными ядрами SiFive Performance P550 с внеочередным выполнением инструкций. Объём кеша L2 составляет 256 Кбайт, кеша L3 — 4 Мбайт. В состав SoC входят графический блок 2D/3D GPU, аппаратный модуль кодирования/декодирования видео, нейропроцессорный движок (NPU), контроллер памяти DDR5 и пр. Отмечается, что новинка обеспечивает ИИ-производительность до 13,3 TOPS. Возможна обработка видеоматериалов формата 8K@50 или 28 каналов 1080р@30. В зависимости от модификации плата несёт на борту 16 или 32 Гбайт оперативной памяти LPDDR5. Вместимость флеш-модуля eMMC составляет 128 Гбайт. В оснащение включены два сетевых порта 1GbE, порт SATA-3, слот PCIe 3.0 х16, пять портов USB 3.2 Gen1, коннектор M.2 E-Key (PCIe 3.0) для комбинированного адаптера Wi-Fi/Bluetooth. Решение выполнено в формате miniDTX с габаритами 203 × 170 мм. Ожидается, что HiFive Premier P550 поступит в продажу на платформе Arrow Electronics в июле 2024 года. Говорится о совместимости с Linux — при создании новинки SiFive сотрудничала с компанией Canonical, отвечающей за развитие Ubuntu. SiFive называет новинку самой высокопроизводительной на сегодняшний день платой на базе RISC-V для разработчиков.

22.10.2023 [17:29], Алексей Степин

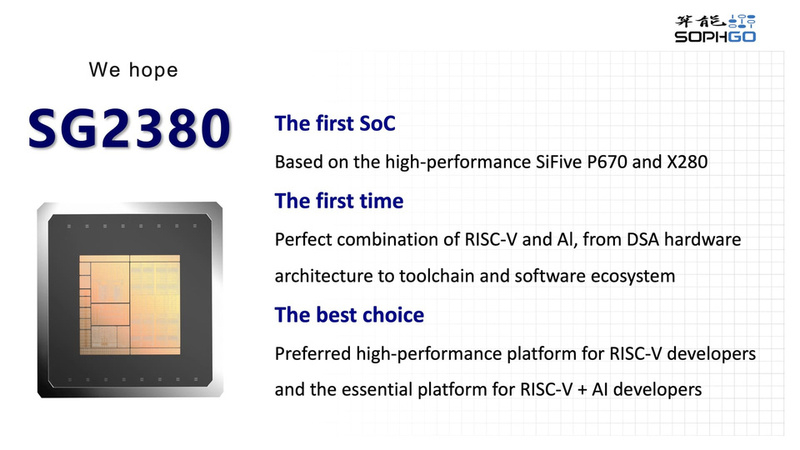

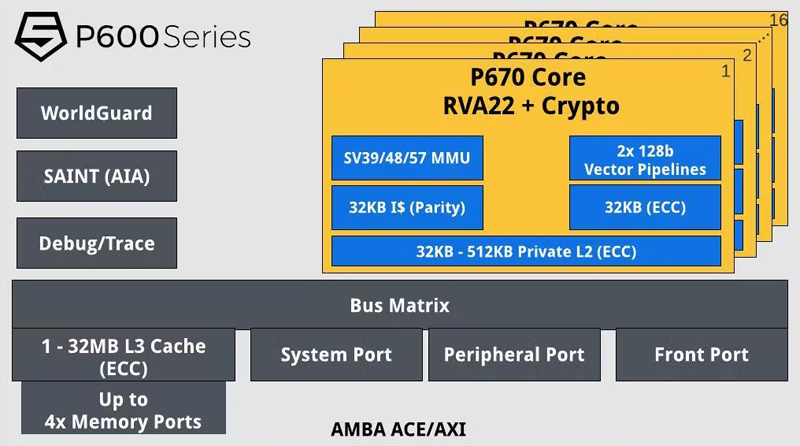

Sophgo представила 16-ядерный процессор SG2380 с архитектурой RISC-V и встроенным ИИ-ускорителемЭкосистема RISC-V наращивает темпы развития: от скромных SBC с одно- и двухъядерными чипами с производительностью уровня Raspberry Pi до вполне «взрослых» многоядерных решений. Одной из компаний, развивающих это направление, является Sophgo. Сейчас Sophgo совместно с Milk-V анонсировала новую плату, оснащённую 16-ядерным процессором SG2380 с интегрированным ИИ-сопроцессором. Ранее Sophgo уже дебютировала с любопытной платой Pioneer, оснащённой 64-ядерным процессором с архитектурой RISC-V и даже показала рабочую станцию разработчика Pioneer Box на её основе. Также компания демонстрировала двухсокетный сервер с 128 ядрами RISC-V. Новинка, Milk-V Oasis, выглядит скромнее, но также весьма небезынтересна. В ней используется 16-ядерный процессор SG2380 с ядрами SiFive Performance P670, работающими на частоте 2,5 ГГц. В дополнение к ним в составе ЦП работает восьмиядерный ИИ-ускоритель на базе SiFive Intelligence X280 с производительностью 20 Топс на вычислениях INT8.

Источник изображений здесь и далее: Sophgo Процессор также располагает собственным GPU Imagination AXT-16-512 с поддержкой Vulkan 1.3, OpenGL 3.0 и OpenGL ES 3.x. Его производительность невысока, всего 0,5 Тфлопс/2 Топс, но для задач, характерных для интегрированной графики, этого достаточно. Видеочасть поддерживает декодирование 10-битного видео в форматах H.265/HEVC, H.264, AV1 и VP9, но аппаратного кодера чип не имеет.  На базе данного процессора Milk-V анонсировала плату Oasis в форм-факторе mini-ITX. Решение обещает до 64 Гбайт памяти LPDDR5 на скорости 5500 МТ/с, поддержку съёмных модулей UFS, полноценный разъём M.2 (PCIe 3.0 x4) и четыре порта SATA. Вывод видео осуществляется с помощью двух портов HDMI (4K@60), порта eDP с поддержкой тачскринов, либо посредством разъёмов MIPI DSI. Сетевая часть представлена двумя портами 2,5GbE, имеются разъёмы M.2 для установки модулей Wi-Fi 6 и 4G/5G-модема. Имеется полноценный слот PCIe x16 (логически PCIe 3.0 x8), 8 разъёмов DIO, 2 разъёма CAN Bus, а также широкий набор портов USB — два версии 3.0, два версии 2.0, два фронтальных версии 2.0 и порт USB-C с возможностью проброса DP. Судя по всему, плата предназначена для периферийных ИИ-платформ, робототехники и иных аналогичного рода задач. Также она может заинтересовать энтузиастов и разработчиков ПО для RISC-V в качестве настольной системы, недорогой альтернативы Pioneer. Стоимость новинки стартует от $120, но доступна она будет ещё не скоро — источники называют III квартал 2024 года. Тем не менее, уже можно оформить предварительный заказ.

23.09.2022 [19:58], Алексей Степин

Google заявила, что использует процессоры SiFive Intelligence X280 на RISC-V вместе со своим TPUАрхитектура RISC-V продолжает понемногу набирать популярность и завоевывать внимание ведущих игроков на рынке информационных технологий. На мероприятии AI Hardware Summit в совместном выступлении ведущего архитектора SiFive и архитектора Google TPU было отмечено, что Google уже использует процессоры с ядрами Intelligence X280. Эти ядра — один из вариантов воплощения архитектуры RISC-V, из продвигаемых SiFive. Анонс Intelligence X280 состоялся ещё в апреле 2021 года, когда SiFive выпустила апдейт 21G1, основной упор в котором был сделан на максимизацию характеристик уже существующих ядер RISC-V в области операций с плавающей запятой.

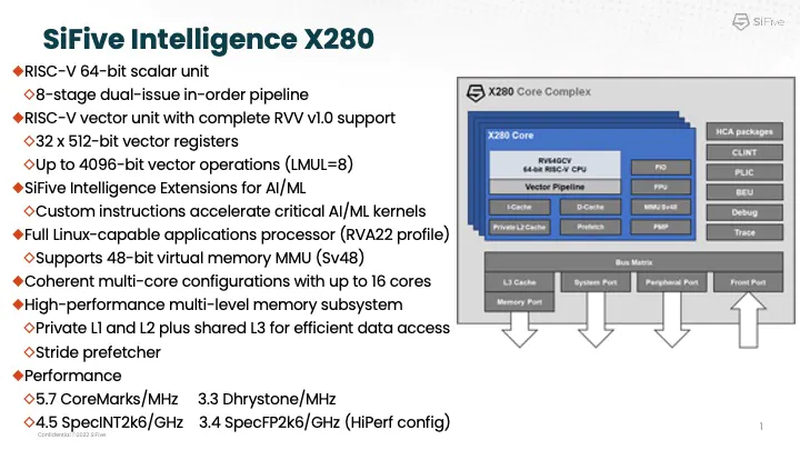

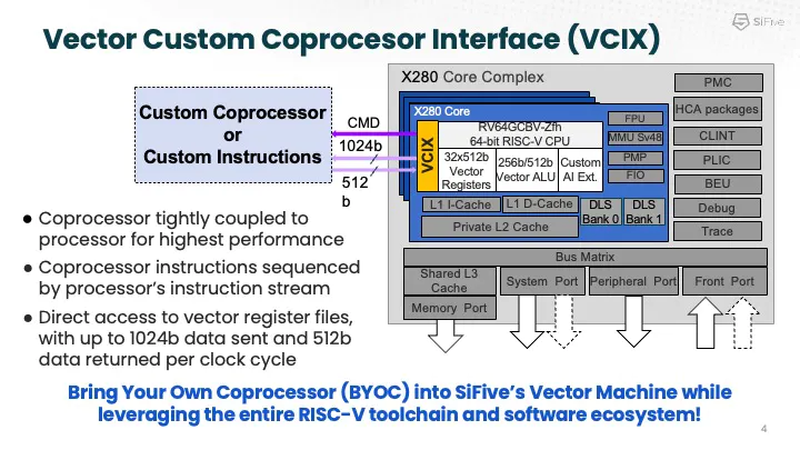

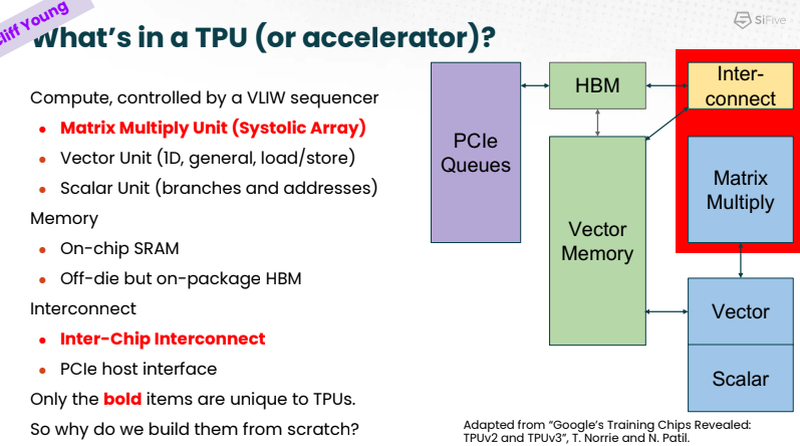

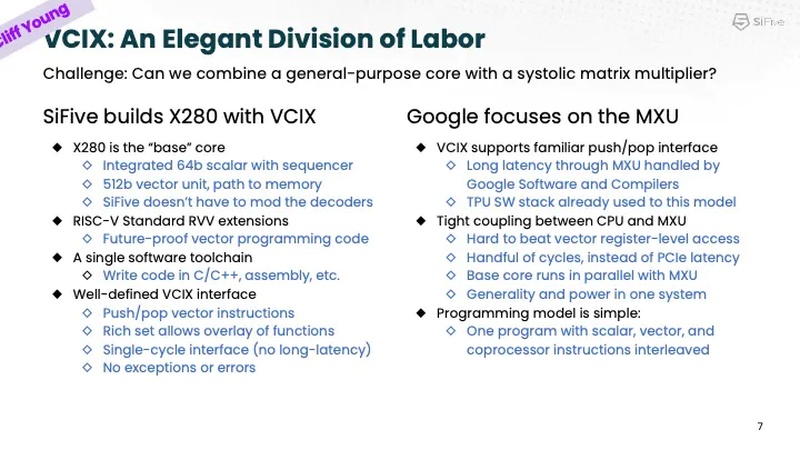

Процессорное ядро Intelligence X280 и его возможности. Источник: SiFive Как следует из названия, данный вариант процессора оптимизирован под задачи машинного интеллекта: ядра RISC-V в нём дополнены векторными конвейерами RISC-V Vector (RVV) с производительностью 4,5 Тфлопс BF16 и 9,2 Топс INT8 на ядро. Одной из самых интересных технологий в Intelligence X280 является интерфейс Vector Coprocessor Interface eXtension (VCIX).

Устройство VCIX. Источник: SiFive Он позволяет подключать внешние ускорители векторных операций напрямую к регистровому файлу X280, минуя основную шину и кеши. Такой подход минимизирует накладные расходы и не требует использования специальных средств при программировании системы, поскольку связка из X280 и подключённого по VCIX ускорителя работает полностью прозрачно в рамках стандартных средств разработки SiFive.

Сильные стороны Google TPU. Источник: SiFive На саммите в Санта-Кларе разработчики SiFive и Google TPU рассказали, что процессоры Intelligence X280 используются в качестве хост-процессоров к ускорителям систолической векторной математики Google MXU; правда, о масштабах внедрения RISC-V в Google сведений приведено не было.

Разделение труда Intelligence X280 и Google TPU. Источник: SiFive Ранее уже появлялась информация, что Google активно тестирует ASIC сторонних разработчиков в связке со своим TPU, в частности, чипы Broadcom, дабы разгрузить его от второстепенных задач и сделать упор на сильных сторонах — матричной математике и быстром интерконнекте. Похоже, SiFive Intelligence X280 решает задачу интеграции подобного рода задач более изящно: как отметил в выступлении Клифф Янг (Cliff Young), архитектор Google TPU, с помощью VCIX можно построить машину, позволяющую усидеть на двух стульях (build a machine that lets you have your cake and eat it too). |

|