Материалы по тегу: risc-v

|

18.06.2025 [11:54], Сергей Карасёв

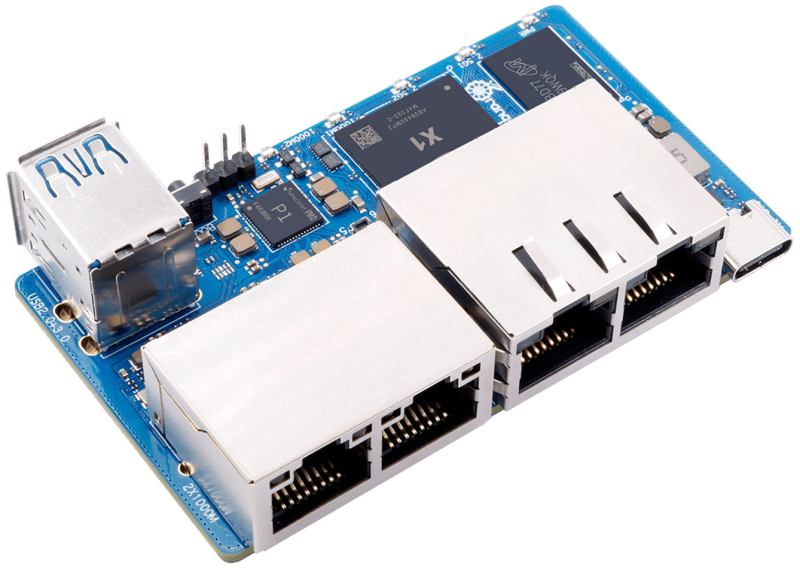

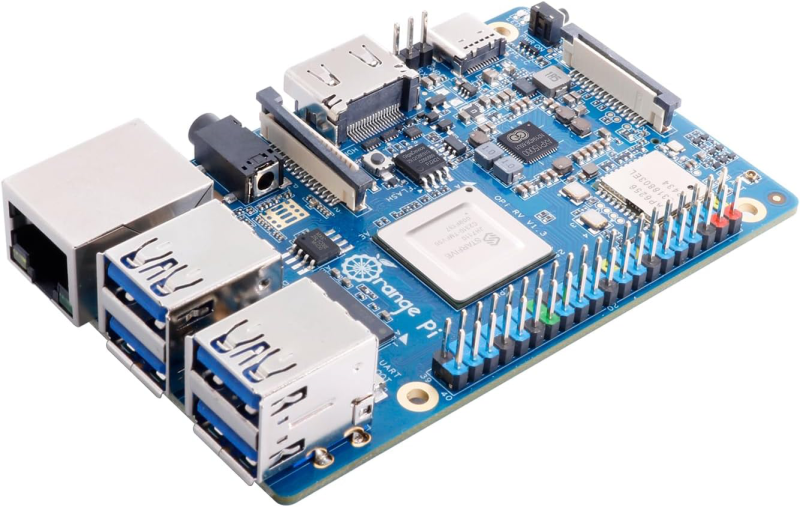

Мини-плата для мини-маршрутизатора: представлена Orange Pi R2S с чипом RISC-VВ семействе одноплатных компьютеров Orange Pi, по сообщению ресурса CNX Software, появилась модель R2S, которую можно использовать для построения различных сетевых устройств, в частности, маршрутизаторов. Новинка уже доступна для заказа по цене от $30. В основу изделия положен процессор Ky X1 с восемью 64-битными ядрами RISC-V (RV64GCVB), функционирующими на частоте до 1,6 ГГц. В состав чипа входят графический ускоритель Imagination IMG BXE-2-32 (819 МГц) с поддержкой OpenGL ES3.2, Vulkan 1.3 и OpenCL 3.0, а также VPU-блок с возможностью декодирования видео H.265, H.264, VP8, VP9, MPEG4, MPEG2 в форматах до 4K@60 Гц и кодирования H.265, H.264, VP8, VP9 в форматах до 4K @ 30 Гц. Процессор также располагает ИИ-ускорителем с производительностью до 2 TOPS (INT8). В зависимости от модификации плата несёт на борту 2, 4 или 8 Гбайт памяти LPDDR4X. Предусмотрены флеш-модуль eMMC вместимостью 8 Гбайт и слот для карты microSD. За сетевые подключения отвечают два порта 2.5GbE на основе контроллеров RealTek RTL8125BG и два порта 1GbE на базе YT8531C-CA: во всех случаях для подключения кабелей служат разъёмы RJ45. Кроме того, имеются по одному порту USB 3.0 и USB 2.0. Питание 5 В / 3 A подаётся через порт USB Type-C. Изделие имеет размеры 79,2 × 46 мм и весит 60 г. Отмечается, что для новинки будут доступны образы OpenWrt 24.10 и Ubuntu 24.04 (ядро Linux 6.6.xx). Стоимость Orange Pi R2S с 2 Гбайт ОЗУ составляет $30, с 4 Гбайт — $40. Цена варианта с 8 Гбайт памяти пока не указывается, но, по всей видимости, она окажется на уровне $50.

28.04.2025 [12:54], Сергей Карасёв

Одноплатный компьютер Muse Pi Pro оснащён чипом RISC-V, адаптерами Wi-Fi 6 и Bluetooth 5.2Китайская компания SpacemiT, по сообщению ресурса CNX Software, выпустила одноплатный компьютер Muse Pi Pro — более компактную модификацию изделия Muse Pi, которое дебютировало в июне 2024 года. Новинка уже доступна для заказа по ориентировочной цене от $122. Как и оригинальная версия, модель Muse Pi Pro несёт на борту процессор SpacemiT M1 с восемью ядрами X60 с архитектурой RISC-V, работающими на частоте до 1,8 ГГц. В состав чипа входят графический ускоритель Imagination IMG BXE-2-32 с поддержкой OpenGL ES3.2, Vulkan 1.2 и OpenCL 3.0, а также VPU-блок с возможностью кодирования/декодирования материалов H.265/H.264 1080p60. Кроме того, имеется нейропроцессорный узел (NPU) с ИИ-производительностью до 2 TOPS (INT8).

Источник изображения: CNX Software Одноплатный компьютер может комплектоваться 8 или 16 Гбайт оперативной памяти LPDDR4X-2400, а также флеш-чипом eMMC 5.1 вместимостью 64 или 128 Гбайт. Есть слот microSD (UHS-II), коннектор M.2 M-Key 2230 для NVMe SSD и коннектор miniPCIe (PCIe 2.1 x1) для сотового модема 4G/5G. В оснащение входят адаптеры Wi-Fi 6 и Bluetooth 5.2, сетевой контроллер 1GbE. Устройство располагает разъёмом HDMI 1.4 (1080p60), четырьмя портами USB 3.0 Type-A и одним портом USB 2.0 Type-C OTG, гнездом RJ45 для сетевого кабеля, интерфейсами MIPI CSI на четыре и две линии, 40-контактной колодкой GPIO и 3,5-мм аудиогнездом. Габариты составляют 85 × 56 мм. Диапазон рабочих температур простирается от -20 до +70 °C у обычной версии и от -40 до +85 °C у индустриального варианта. Питание (5/9/12 В, до 3 A) подаётся через разъём USB Type-C. Говорится о совместимости с Bianbu Desktop, Ubuntu, OpenKylin, Deepin, Fedora и др.

23.04.2025 [11:20], Сергей Карасёв

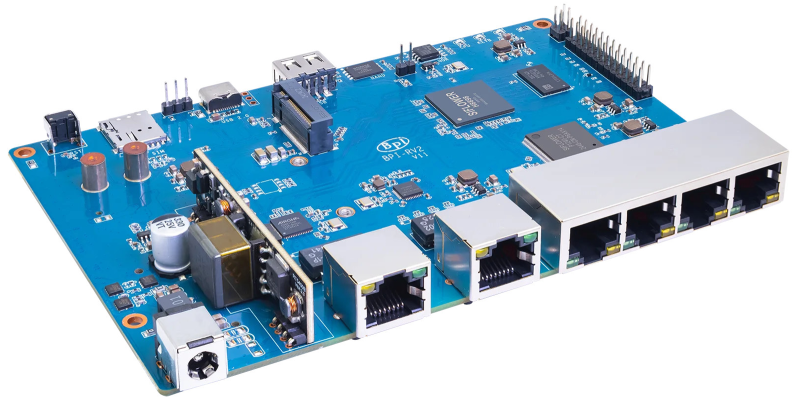

Плата Banana Pi BPI-RV2 для компактных маршрутизаторов оснащена чипом RISC-VВ ассортименте Banana Pi, по сообщению ресурса CNX-Software, появилась плата BPI-RV2, предназначенная для построения компактных маршрутизаторов. Изделие доступно для заказа по ориентировочной цене от $35. Основой новинки служит процессор Siflower SF21H8898 с четырьмя 64-битядрами с архитектурой RISC-V, работающими на тактовой частоте до 1,25 ГГц. Объём оперативной памяти DDR3 составляет 512 Мбайт. Предусмотрено 128 Мбайт памяти SPI NAND Flash (для U-Boot и Linux), а также 16 Мбайт памяти SPI NOR Flash (U-Boot и Linux) с защитой от записи по умолчанию. Плата располагает коннектором M2 Key-B (PCIe 2.0 x1 + USB 2.0) для NVMe SSD или модема 5G (плюс разъём для карты Nano SIM), а также слотом mini PCIe (PCIe 2.0 x1) для адаптера Wi-Fi или сетевой карты. Есть 26-контактная колодка GPIO, разъём USB 2.0 Type-A и порт USB Type-C. Изделие оборудовано шестью сетевыми портами RJ45, из которых пять поддерживают стандарт 1GbE, а один — 2.5GbE. Опционально может быть реализована поддержка 802.3at/af PoE (через порт 2.5GbE). Новинка имеет размеры 148 × 100,5 мм. Питание (12 В / 2 A) подаётся через коннектор 5.5/2.1 мм. Плата Banana Pi BPI-RV2 использует форк OpenWrt (Linux 5.10). Базовая версия изделия предлагается за $34,5, а доплатив ещё $4, можно приобрести вариант с PoE. На текущий момент для платы нет специализированного корпуса, позволяющего получить полноценный маршрутизатор. Но по габаритам решение идентично модели Banana Pi BPI-R3, для которой предлагается недорогой металлический корпус.

21.04.2025 [08:46], Сергей Карасёв

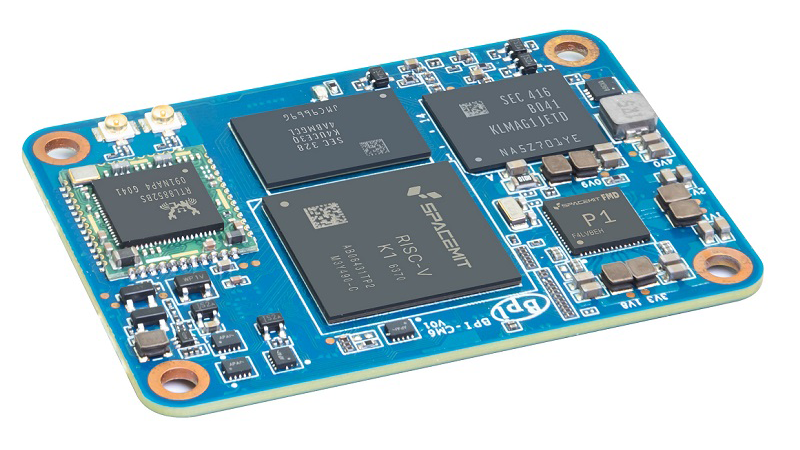

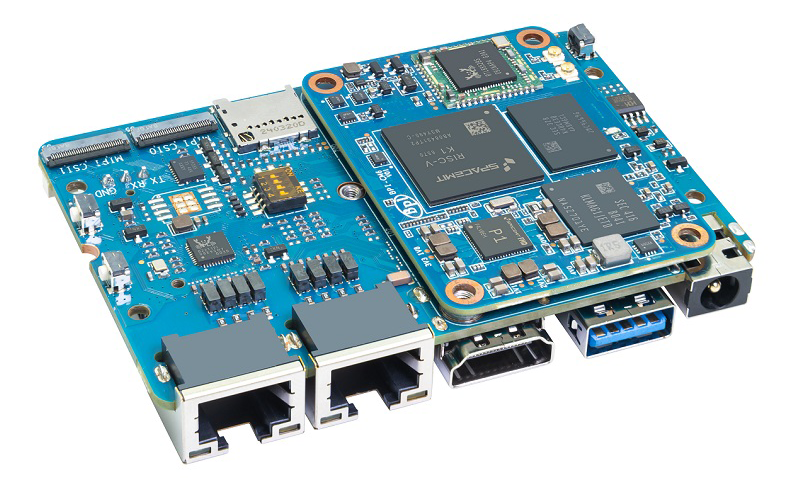

Представлен модуль Banana Pi BPI-CM6 — аналог Raspberry Pi CM4 на базе RISC-VВ ассортименте Banana Pi появился вычислительный модуль BPI-CM6 — это альтернатива Raspberry Pi CM4, выполненная на процессоре с открытой архитектурой RISC-V вместо Arm. Новинка подходит для создания систем промышленного контроля и автоматизации, NAS-устройств, робототехники, периферийных решений и пр. По форме, габаритам и расположению коннекторов новинка идентична Raspberry Pi CM4. Задействован чип SpacemiT K1, который объединяет восемь 64-битных ядер RISC-V, графический блок Imagination BXE-2-32 с поддержкой OpenCL 3.0, OpenGL ES3.2 и Vulkan 1.3, а также нейропроцессорный узел (NPU) с производительностью до 2 TOPS для ускорения ИИ-операций.

Источник изображений: Banana Pi Модуль Banana Pi BPI-CM6 располагает 8 Гбайт оперативной памяти LPDDR4 (максимум 16 Гбайт) и чипом eMMC вместимостью 16 Гбайт (максимум 128 Гбайт). Реализована поддержка Bluetooth и Wi-Fi, PCIe 2.1 (5 линий), USB 3.0 и USB 2.0 (×2), HDMI 1.4, MIPI DSI и MIPI CSI (×3). Размеры составляют 40 × 55 мм. Диапазон рабочих температур простирается от -40 до +85 °C. Говорится о совместимости с Ubuntu Linux.  Для новинки доступна сопутствующая интерфейсная плата, которая содержит по одному разъёму HDMI, USB 3.0 Type-A, USB 2.0 Type-A и USB Type-C OTG, два сетевых порта 1GbE RJ45 и слот для карты microSD. Кроме того, есть два коннектора M.2 M-Key (PCIe х2) для подключения SSD, 26-контактная колодка GPIO, два интерфейса MIPI CSI (4 линии) и один интерфейс MIPI DSI (4 линии). Питание (12 В) подаётся через DC-коннектор. Габариты — 56 × 85 мм.

05.04.2025 [10:35], Сергей Карасёв

Представлен первый в Китае высокопроизводительный процессор RISC-V для серверов — чип LingyuКитайская компания RiVAI Technologies, по сообщению ресурса Tom's Hardware, представила первый высокопроизводительный серверный процессор с открытой архитектурой RISC-V, полностью разработанный в КНР. Презентация изделия под названием Lingyu состоялась в Шэньчжэне: появление чипа отражает стремление страны к снижению зависимости от зарубежных изделий в условиях усиливающихся санкций со стороны США. Чип Lingyu насчитывает в общей сложности 40 ядер. Это 32 универсальных вычислительных ядра (CPU) и восемь специализированных ядер (LPU), предназначенных для нагрузок, связанных с ИИ, включая работу с большими языковыми моделями (LLM). Такая конфигурация ориентирована на достижение баланса между производительностью и энергоэффективностью, благодаря чему снижается общая стоимость владения (TCO). Прочие характеристики процессора пока не раскрываются. Основателем компании RiVAI Technologies является Чжанси Тан (Zhangxi Tan). Он получал образование под наставничеством Дэвида Паттерсона (David Patterson) — американского учёного в области информатики, профессора Калифорнийского университета в Беркли (UC Berkeley) и лауреата премии Тьюринга 2017 года. Паттерсон, разработавший в 1990–2000 гг. несколько вариантов RISC-архитектур, выступает в качестве консультанта RiVAI Technologies. Отмечается, что RiVAI Technologies заключила партнёрские соглашения с более чем 50 компаниями, включая Lenovo и SenseTime, с целью развития экосистемы вокруг своих чипов RISC-V. Сотрудничество направлено на внедрение Lingyu в различных отраслях. Предполагается, что усилия будут способствовать дальнейшему развитию RISC-V в Китае. В целом, КНР ведёт активные исследования и разработки в области RISC-V. В частности, ранее ряд китайских компаний, включая T-Head (принадлежит гиганту Alibaba Group Holding), Shanghai Shiqing Technology, Juquan Optoelectronics, Xinsiyuan Microelectronics и StarFive, сформировали патентный альянс в сфере RISC-V. Кроме того, Пекин планирует запустить государственную программу с целью стимулирования широкого использования RISC-V по всей стране. Разработкой RISC-V-процессоров занимается Китайская академия наук.

04.04.2025 [10:10], Сергей Карасёв

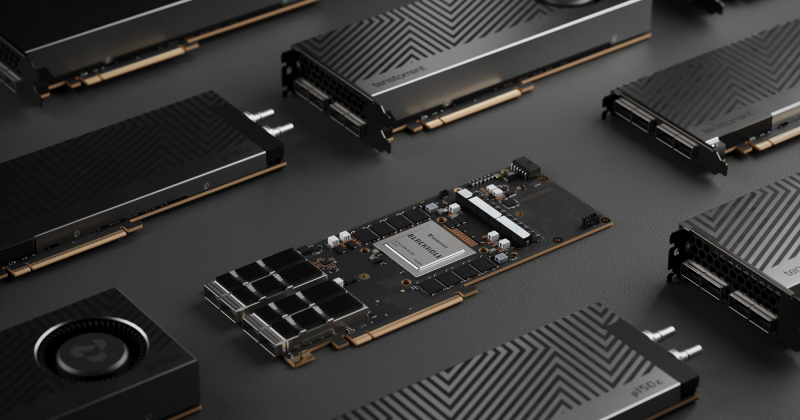

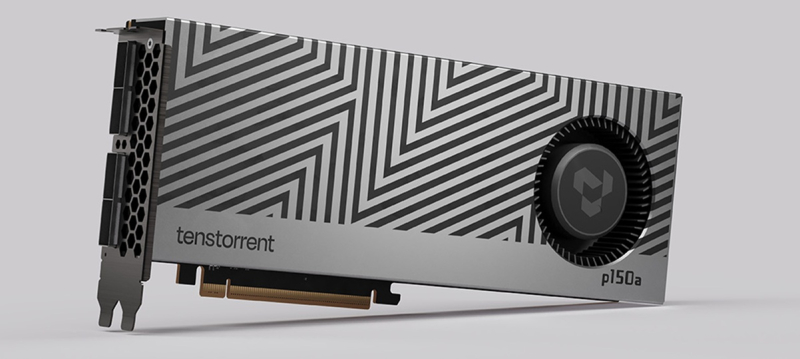

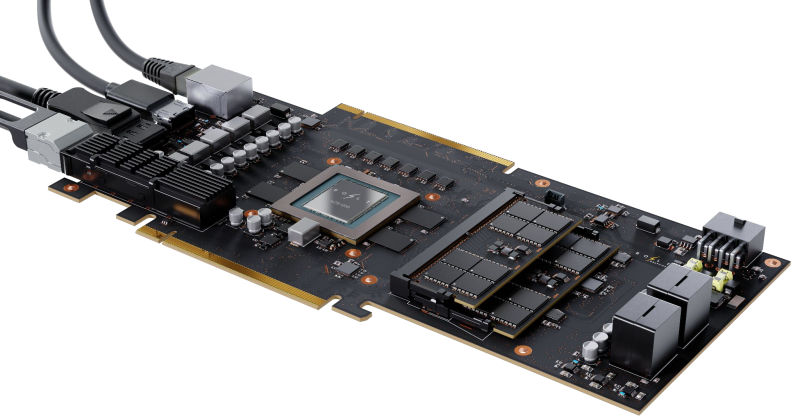

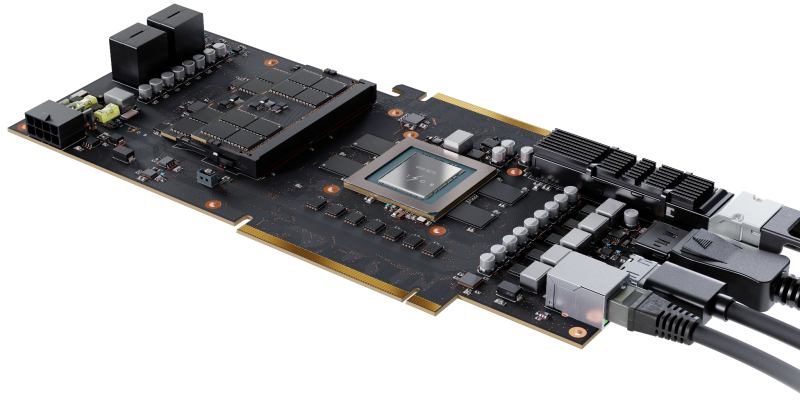

Tenstorrent представила ИИ-ускорители Blackhole на архитектуре RISC-VКанадский стартап Tenstorrent анонсировал ИИ-ускорители семейства Blackhole, выполненные в виде двухслотовых карт расширения с интерфейсом PCI Express 5.0 x16. Кроме того, дебютировала рабочая станция TT-QuietBox, оборудованная этими изделиями. Напомним, ранее Tenstorrent выпустила ИИ-ускорители Wormhole с 72 и 128 ядрами Tensix, каждое из которых содержит пять ядер RISC-V. Объём памяти GDDR6 составляет соответственно 12 и 24 Гбайт. Производительность достигает 262 и 466 Тфлопс на операциях FP8. В семейство Blackhole вошли модели p100a и p150a/p150b. Первая располагает 120 ядрами Tensix, 16 «большими» ядрами RISC-V, 180 Мбайт памяти SRAM и 28 Гбайт памяти GDDR6 с пропускной способностью 448 Гбайт/с. Изделия p150a/p150b оснащены 140 ядрами Tensix, 16 «большими» ядрами RISC-V, 210 Мбайт памяти SRAM и 32 Гбайт памяти GDDR6 с пропускной способностью 512 Гбайт/с. Энергопотребление у всех ускорителей достигает 300 Вт. Тактовая частота ИИ-блока — 1,35 ГГц. Габариты карт составляют 42 × 270 × 111 мм. Модели p100a и p150a наделены активным охлаждением, версия p150b — пассивным. При этом ускорители p150a/p150b оборудованы четырьмя разъёмами QSFP-DD 800G. Рабочая станция TT-QuietBox несёт на борту четыре карты Blackhole p150. Основой служат материнская плата ASRock Rack SIENAD8-2L2T и процессор AMD EPYC 8124P (Siena) с 16 ядрами (32 потока) с тактовой частотой до 3 ГГц. Объём оперативной памяти DDR5-4800 ECC RDIMM равен 256 Гбайт (8 × 32 Гбайт). Установлен SSD вместимостью 4 Тбайт с интерфейсом PCIe 4.0 x4 (NVMe). Присутствуют по два сетевых порта 10GbE RJ45 (контроллер Intel X710-AT2) и 1GbE RJ45 (Intel i210), четыре порта USB 3.1 Gen1 Type-A (по два спереди и сзади), аналоговый разъём D-Sub.  Ускоритель Blackhole p100 предлагается по цене около $1000, тогда как обе модификации Blackhole p150 оценены в $1300. Рабочая станция TT-QuietBox Blackhole обойдётся в $12 тыс.

01.04.2025 [10:27], Сергей Карасёв

Одноплатный компьютер Orange Pi RV получил процессор RISC-V и 8 Гбайт оперативной памятиКоманда Orange Pi, как сообщает CNX Software, продолжает расширять ассортимент одноплатных компьютеров на процессорах с открытой архитектурой RISC-V. Вслед за изделиями Orange Pi 4A и Orange Pi RV2 в продажу поступила модель Orange Pi RV, которую можно приобрести по цене от $30. Новинка базируется на чипе StarFive JH7110, который содержит четыре ядра RISC-V (RV64GC) с частотой 1,5 ГГц и графический ускоритель Imagination BXE-4-32 с поддержкой OpenCL 1.2, OpenGL ES 3.2, Vulkan 1.2. Имеется VPU-блок с возможностью декодирования материалов H.264/H.265 4Kp60 и кодирования видео H.265 1080p30. Объём оперативной памяти LPDDR4-2800 может составлять 2, 4 или 8 Гбайт. Предусмотрены коннектор M.2 M-Key 2280 (PCIe 2.0 x1) для NVMe SSD и слот для карты microSD (SDIO 3.0). В оснащение входят адаптеры Wi-Fi 5.0 и Bluetooth 5.0 LE (Ampak AP6256), а также сетевой контроллер 1GbE (YT8531C) с разъёмом RJ45. Есть четыре порта USB 3.0, интерфейс HDMI 2.0 с поддержкой видео 4K (30 Гц), стандартное аудиогнездо 3,5 мм и разъём USB 2.0 Type-C, который служит в том числе для подачи питания (5 В / 4 A). Упомянуты 40-контактная колодка GPIO (UART, I2C, SPI, PWM, GND), коннектор MIPI DSI (две линии). Одноплатный компьютер имеет размеры 89 × 56 мм и весит 54 г. Для модели Orange Pi RV заявлена поддержка Linux. За $30 можно приобрести вариант с 2 Гбайт ОЗУ, тогда как модификации с 4 и 8 Гбайт памяти обойдутся в $40 и $50 соответственно. Для изделия будет доступен полный набор документации, включая схематику.

29.03.2025 [10:11], Алексей Степин

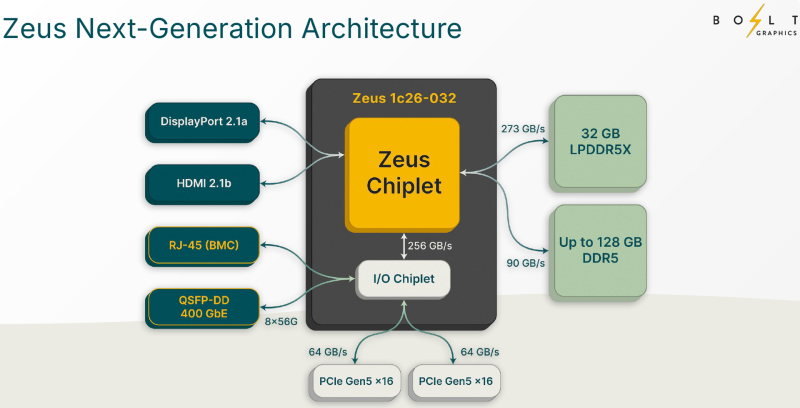

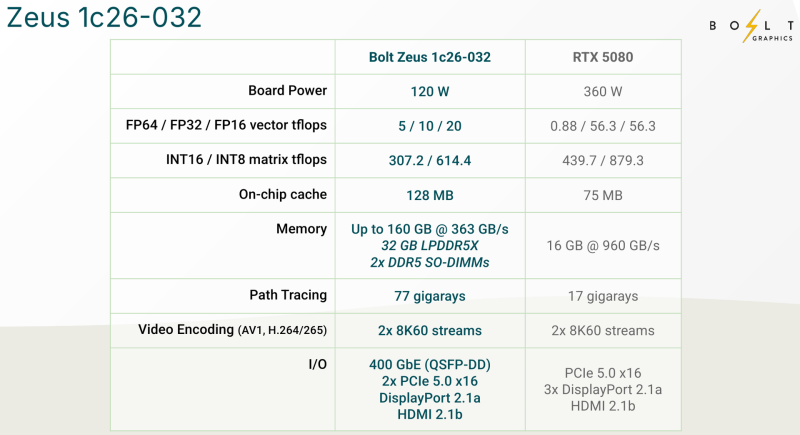

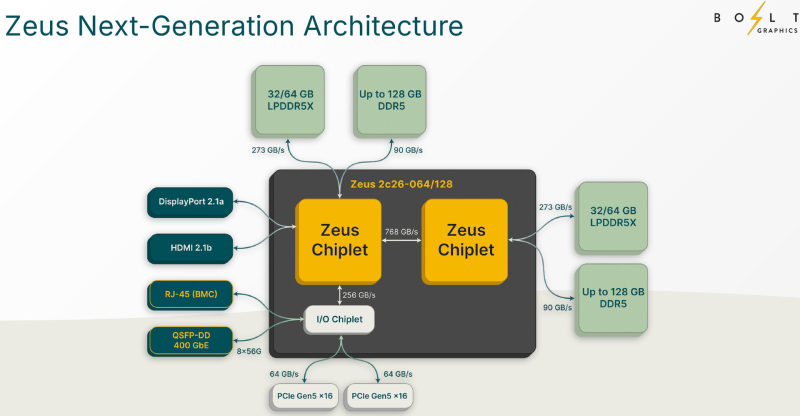

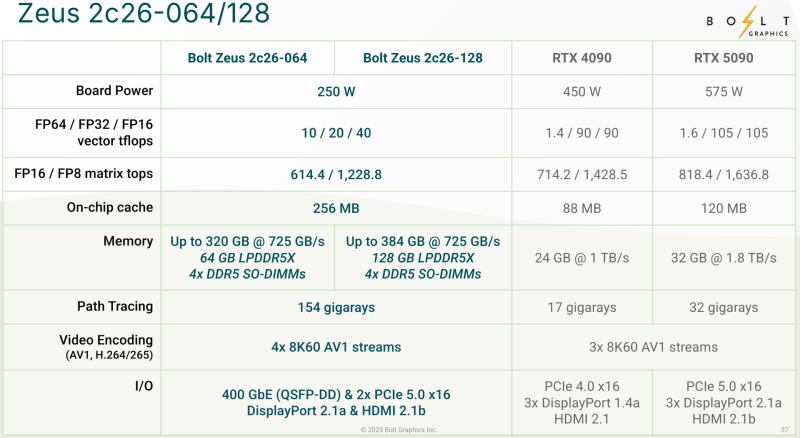

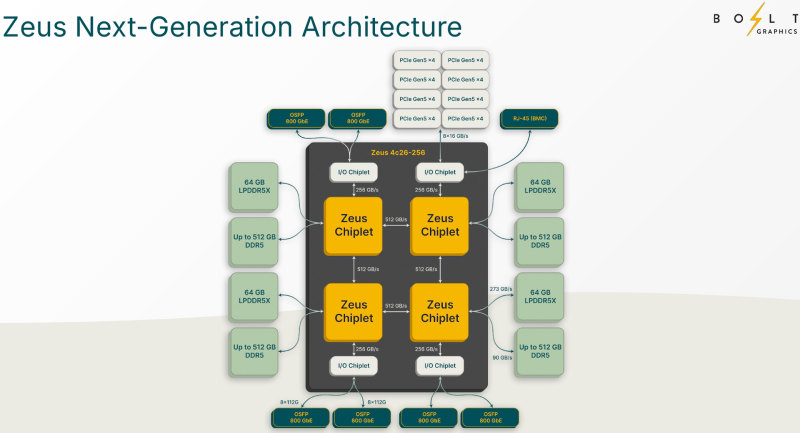

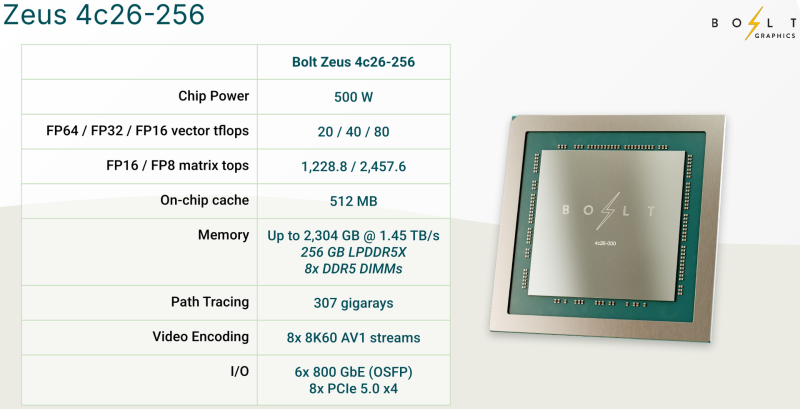

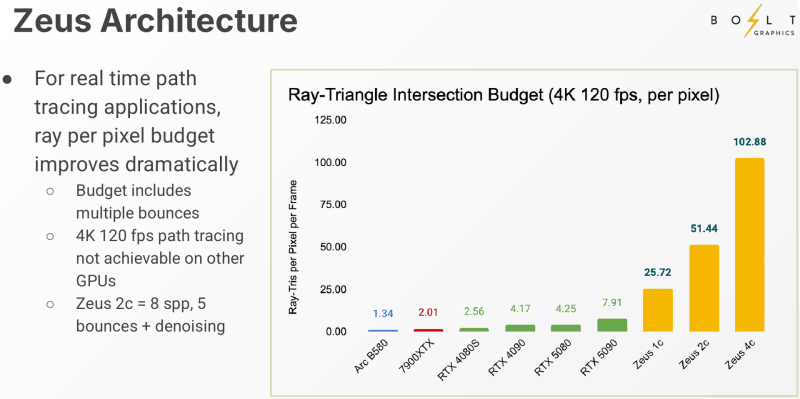

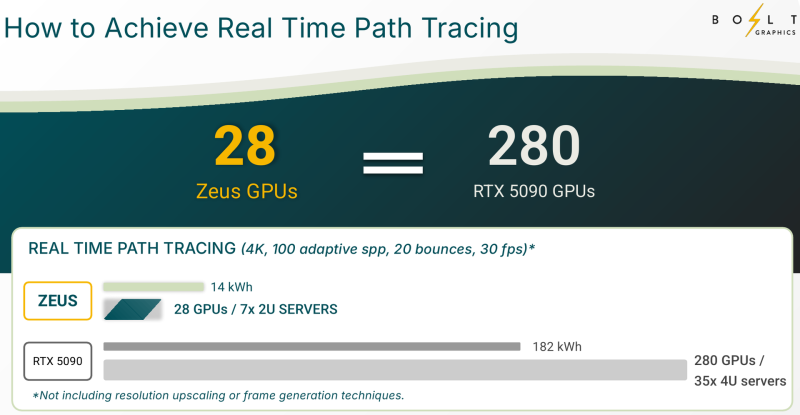

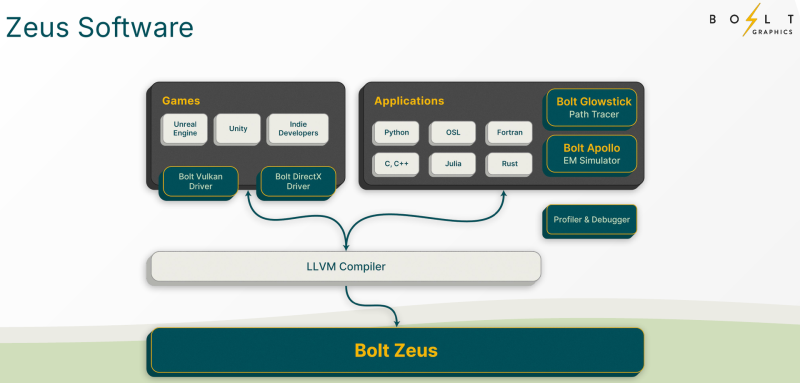

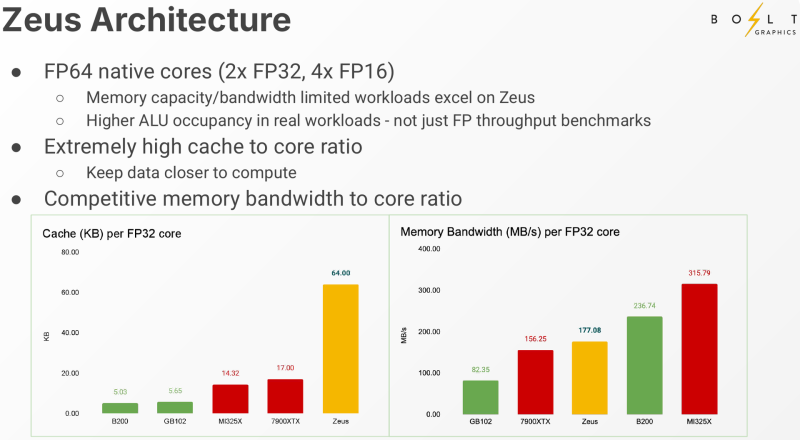

Bolt Graphics анонсировала универсальную видеокарту со слотами SO-DIMM, которая может потягаться с RTX 5080Все современные графические ускорители предлагаются с жёстко заданным при производстве объёмом видеопамяти, а в наиболее производительных моделях память типа HBM вообще интегрирована на одной с основным кристаллом подложке. Однако требования к объёму памяти в последнее время растут быстрее, а за дополнительный объём вендор просят всё больше. Кардинально иной подход предлагает компания Bolt Graphics, недавно анонсировавшая серию ускорителей Zeus. Несмотря на «ИИ-пандемию», Bolt Graphics в своём анонсе не делает упор на искусственный интеллект, а называет Zeus первым GPU, специально созданным для целей HPC, рендеринга, трассировки лучей и даже компьютерных игр. Что интересно, в основе Zeus лежит не некая закрытая архитектура: скалярная часть нового GPU построена на базе спецификации RISC-V RVA23, векторная представлена FP64 ALU на базе несколько модифицированной RVV 1.0. Прочие функции реализованы путём кастомных расширений и отдельных блоков-ускорителей. Все они пользуются общим кешем объёмом 128 Мбайт. Дополняет картину блок телеметрии и внутренний интерконнект для общения с другими вычислительным блоками. Используется чиплетный подход. Базовый «строительный блок» Zeus 1c26-032 включает GPU-чиплет, который соединён с 32 Гбайт набортной памяти LPDDR5x (273 Гбайт/с) и контроллером внешней памяти DDR5 (90 Гбайт/с), т.е. при желании можно установить ещё 128 Гбайт RAM (два модуля SO-DIMM). В GPU-чиплет встроены контроллеры DisplayPort 2.1a и HDMI 2.1b, а с внешним миром он общается посредством IO-чиплета, с которым он соединён 256-Гбайт/с каналом. IO-чиплет предлагает необычный набор портов. Помимо сразу двух интерфейсов PCIe 5.0 x16 (64 Гбайт/с каждый) имеется выделенный порт RJ-45 для BMC и 400GbE-порт QSFP-DD. Наконец, есть аппаратный блок видеокодирования, способный справиться с двумя потоками 8K@60 AV1/H.264/H.265. Заявленный уровень производительности в векторных FP64/FP32/FP16-вычислениях составляет 5/10/20 Тфлопс, а в матричных INT16/INT8 — 307,2/614,4 Топс. Аппаратный блок ускорения лучей (path tracing) выдаёт до 77 гигалучей. Для сравнения: NVIDIA RTX 5090 способна выдавать 32 гигалуча, а FP64-производительность составляет 1,6 Тфлопс. В то же время в расчётах пониженной точности актуальные решения NVIDIA всё равно быстрее Zeus 1c26-032. Однако у новинки есть важное преимущество — её уровень TDP составляет всего 120 Вт. Второй интерфейс PCIe 5.0 x16 можно использовать для прямого объединения двух карт. Вариант ускорителя с двумя чиплетами носит название Zeus 2c26-064/128, а с четырьмя — 4c26-256. Последние числа обозначают объём распаянной памяти LPDDR5X. Что касается расширяемой памяти, то количество доступных разъёмов SO-DIMM также зависит от модели и составляет до восьми, так что во флагманской конфигурации базовые 256 Гбайт LPDDR5x можно дополнить аж 2 Тбайт DDR5. Производительность с увеличением количеств GPU-чиплетов растёт практически пропорционально, но есть некоторые другие нюансы. Так, в Zeus 2c26-064 и Zeus 2c26-128 (оба варианта имеют TDP 250 Вт) есть только один IO-чиплет, а GPU-чиплеты объединены шиной со скоростью 768-Гбайт. Zeus 4c26-256 имеет сразу четыре I/O чиплета в составе, которые дают восемь контроллеров PCIe 5.0 x4 (один чиплет, совокупно 32 линии) и шесть 800GbE-портов OSFP (три чиплета). Между собой GPU-чиплеты объединены шиной со скоростью 512-Гбайт/с. Каждый из них соединён с собственным IO-чиплетом на скорости 256 Гбайт/с. Теплопакет флагмана составляет 500 Ватт, ускоритель, если верить Bolt Graphnics, развивает 20 Тфлопс в режиме FP64, почти 2500 Топс на вычислениях FP8 и способен обрабатывать до 307 гигалучей. Разработчики явно заложили в своё детище широкие возможности кластеризации, о чём свидетельствует наличие мощной сетевой подсистемы. Поддерживаются как скромные конфигурации из двух GPU, соединённых непосредственно по Ethernet 400GbE, так и масштабные системы уровня стойки, содержащей 80 плат Zeus 4c26-256, соединённых как с коммутатором, так и напрямую друг с другом. Такой кластер потребляет 44 кВт, но зато способен обеспечивать запуск крупных физических симуляций или обучение ИИ моделей за счёт огромного массива общей памяти, составляющего 160 Тбайт. Вычислительная производительность такого кластера достигает 1,6 Пфлопс в режиме FP64 и 196 Попс в режиме FP8. Одной из особенностей новинок является трассировщик лучей Glowstick, способный работать в режиме реального времени практически во всех современных пакетах 3D-моделирования или видеоредактирования, таких как Maya, 3ds Max, Blender, SketchUp, Houdini и Nuke. Он будет дополнен фирменной библиотекой Bolt MaterialX, содержащей более 5000 текстур высокого качества. А благодаря поддержке стандарта OpenUSD он сможет легко интегрироваться в любую цепочку рендеринга и пост-обработки. Также запланирован электромагнитный симулятор Bolt Apollo. Обещаны фирменные драйверы Vulkan/DirectX и SDK с использованием LLVM. Ранний доступ к комплектам разработчика Bolt Graphics наметила на IV квартал текущего года. В III квартале 2026 года должны появиться 2U-серверы на базе Zeus, а массовые поставки серверов и PCIe-карт начнутся не ранее IV квартала того же года. Пока сложно сказать, насколько хорошо новая архитектура себя проявит, но если верить предварительным тестам Zeus, выигрыш в сравнении с существующими ускорителями существенен, особенно в энергопотреблении.

18.03.2025 [10:09], Сергей Карасёв

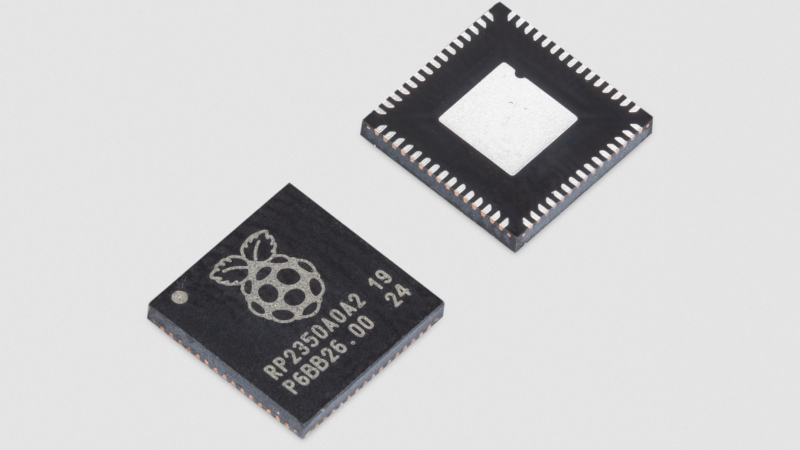

Микроконтроллер Raspberry Pi RP2350 поступил в продажу по цене от $0,8Компания Raspberry Pi объявила о начале продаж микроконтроллера RP2350, который является основой крошечной платы Raspberry Pi Pico 2, дебютировавшей в августе прошлого года. Кроме того, RP2350 применяется в ряде других изделий, например, в составе микроплаты Pico W5. Микроконтроллер содержит по два ядра Arm Cortex-M33 и RISC-V Hazard3 с тактовой частотой 150 МГц. Нужный кластер выбирается при инициализации изделия, то есть, использовать одновременно блоки Cortex-M33 и RISC-V нельзя. Устройство располагает 520 Кбайт памяти SRAM. За безопасность отвечают средства Arm TrustZone.

Источник изображения: Raspberry Pi Raspberry Pi RP2350 обеспечивает поддержку 2 × UART, 2 × SPI, 2 × I2C, 24 × PWM и пр. Изделие на программном уровне совместимо с микроконтроллером Raspberry Pi RP2040. Предусмотрены варианты исполнения RP2350A (QFN-60; 7 × 7 мм; 30 × GPIO) и RP2350B (QFN-80; 10 × 10 мм; 48 × GPIO). Кроме того, к выпуску готовятся модификации RP2354A и RP2354B в аналогичных исполнениях, дополненные 2 Мбайт флеш-памяти Stacked Flash. При заказе по отдельности стоимость RP2350A и RP2350B составляет соответственно $1,1 и $1,2. Микроконтроллеры также можно приобрести оптом в катушках размером 7" и 13": в первом случае изделия обойдутся в $0,9 и $1,0 за единицу (500 штук в катушке), во втором — в $0,8 и $0,9 за штуку (3400 и 2500 единиц в катушке). Компания Raspberry Pi предоставляет для микроконтроллеров подробную документацию, которая поможет в реализации различных проектов: это могут быть устройства IoT, встраиваемые системы промышленного класса, потребительские продукты и пр.

12.03.2025 [20:37], Владимир Мироненко

Евросоюз потратит €240 млн на создание трёх RISC-V чиплетов для суперкомпьютеров в рамках проекта DARE

eurohpc

hardware

hpc

risc-v

европа

ии

импортозамещение

инвестиции

суперкомпьютер

ускоритель

финансы

чиплеты

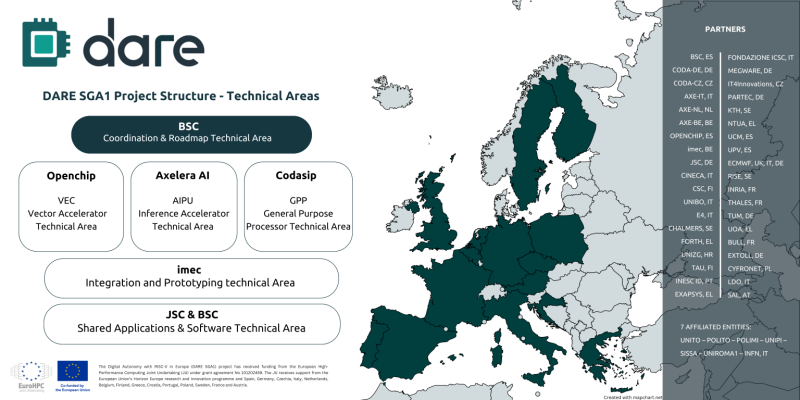

Digital Autonomy with RISC-V in Europe (DARE), крупнейший проект по разработке чипов из когда-либо финансируемых Европейским союзом, созданный с целью укрепления технологического суверенитета Европы в области высокопроизводительных вычислений (HPC) и искусственного интеллекта (ИИ), официально начал первый этап DARE SGA1, на реализацию которого выделено €240 млн ($262 млн), сообщается на сайте проекта. Европа и Китай делают ставку на RISC-V. Финансирование инициативы обеспечат 38 участников, включая ИТ-компании, исследовательские институты и университеты по всей Европе. Проект поддерживается EuroHPC JU и координируется Барселонским суперкомпьютерным центром (BSC-CNS). Последний имеет богатый опыт разработки чипов RISC-V и суперкомпьютерных систем. Половина инвестиций в проект DARE будет предоставлена Европейской комиссией через EuroHPC, а другая половина поступит напрямую от европейских партнёров, включая €34 млн от Министерства науки, инноваций и университетов Испании. Рассчитанный на три года DARE SGA1 является первым этапом шестилетней инициативы DARE. Цель — создание полноценного независимого европейского суперкомпьютерного программно-аппаратного стека для HPC и ИИ, включая чипы, системы на основе чиплетов и ПО. Инициатива направлена на удовлетворение стратегической потребности Европы в цифровом суверенитете и получения полного контроля над критической вычислительной инфраструктурой. Проектом DARE SGA1 предусмотрена разработка трёх чиплетов на основе архитектуры RISC-V, каждый из которых будет выполнять критически важную функцию в вычислениях HPC и ИИ:

В дополнение к указанным компаниям в качестве технических лидеров названы imec и Юлихский исследовательский центр (JÜLICH Supercomputing centre, JSC), которые будут продвигать ключевые инновации в рамках проекта. Помимо координации усилий, BSC также возглавит разработку планов и будет участвовать в разработке программных и аппаратных решений. Изготавливаться чиплеты будут по технологии CMOS с использованием современных техпроцессов. Axelera получит на разработку до €61 млн при условии выполнения различных задач в течение следующих трёх лет, рассказал ресурсу EE Times генеральный директор Axelera Фабрицио дель Маффео (Fabrizio del Maffeo). Хотя нынешний чип Axelera Metis AIPU предназначен для периферийных систем, дель Маффео сказал, что разрабатываемый в рамках DARE продукт на основе чиплетов не несёт кардинальные изменения, речь скорее о масштабировании. Codasip в прошлом году анонсировала 64-бит чип X730 на базе RISC-V с архитектурной защитой CHERI. По данным The Next Platform, за последнее десятилетие компания привлекла $34,6 млн общего финансирования, включая средства в рамках различных инициатив ЕС, а также посевной раунд в размере $2,5 млн в 2016 году и раунд A в размере $10 млн в 2018 году. |

|