Материалы по тегу: pci express 6.0

|

18.06.2024 [22:45], Алексей Степин

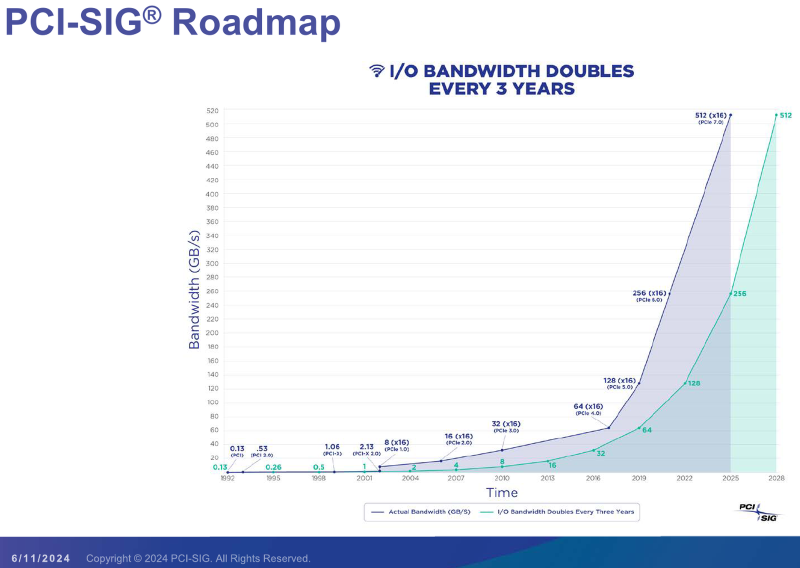

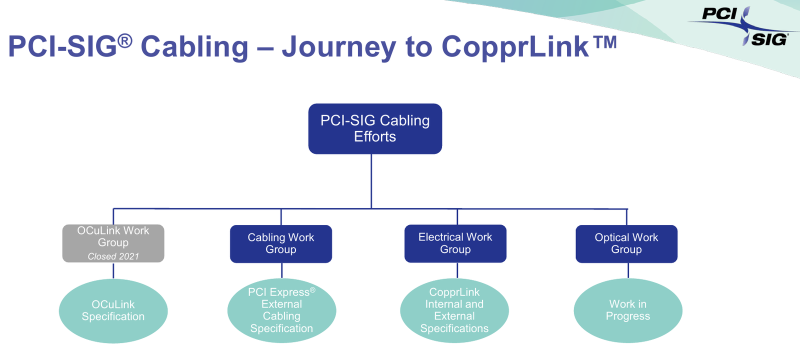

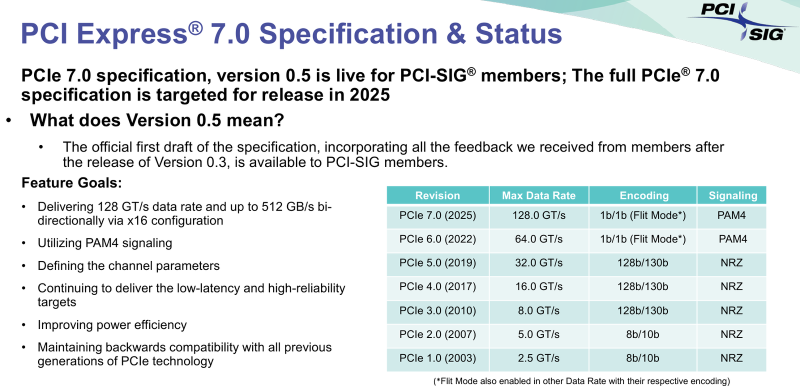

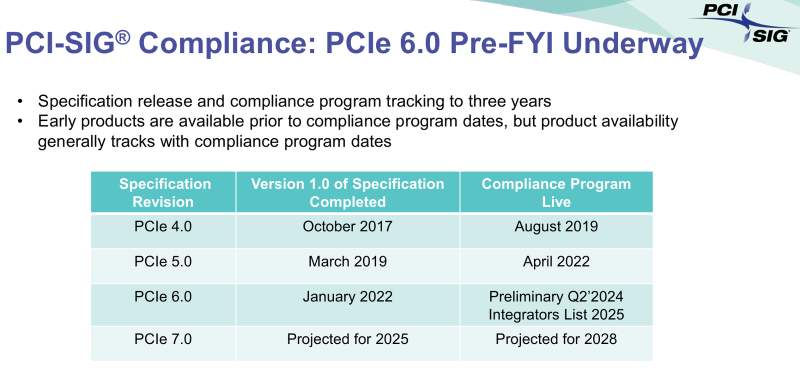

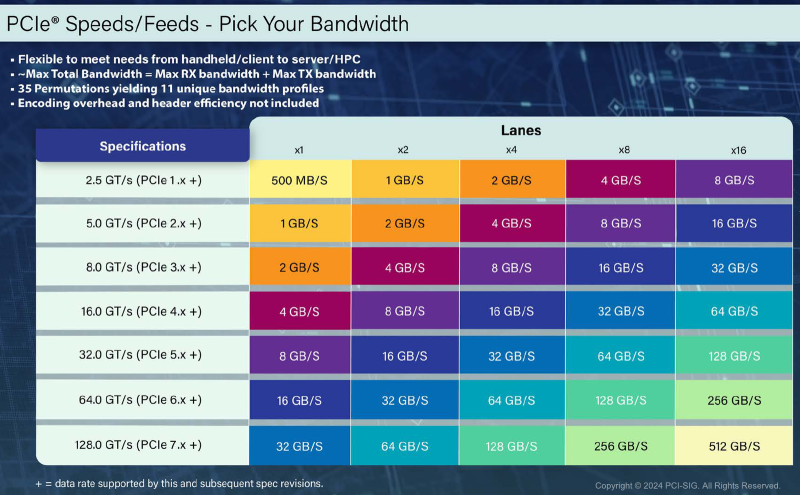

Обещанного три года ждут: разработка и внедрение новых стандартов PCI Express не ускорятся, но PCI-SIG не видит в этом проблемыНа недавно прошедшей конференции PCI-SIG Developers Conference 2024 вице-президент группы, Ричард Соломон (Richard Solomon) рассказал о разработке новых версий стандарта PCI Express. Создание новых стандартов вышло на устоявшийся трехлётний цикл, но в данном случае имплементация и выход на массовый рынок не равны собственно разработке очередной версии PCIe. Приблизительно за три года PCI-SIG успевает разработать, внести корректировки, согласовать все нюансы со всеми участниками консорциума и опубликовать спецификации нового стандарта. Но после этого необходимо получить первые образцы «кремния» с его поддержкой и провести все необходимые квалификационные процедуры. Одна только фаза «тестирования на соответствие» (FYI, First Year Inventory Compliance Program) занимает полгода. Главной причиной достаточно длительного цикла, отметил вице-президент PCI-SIG, является время от окончания работы над спецификациями до получения готовых ASIC, без которых невозможно начать полномасштабное тестирование. Таким образом, формально появившийся в начале 2022 года стандарт PCIe 6.0 лишь в июне 2024 года добрался до фазы FYI. При этом первый дизайн (только на бумаге, конечно) IP-блоков для PCIe 6.0 появился ещё даже до финализации стандарта. Более того, спецификации PCIe 6.0 в скором времени снова будут обновлены для поддержки нового стандарта оптических соединений, которые, впрочем, не заменят, а дополнят традиционные медные соединения. Финализация правок ожидается в декабре текущего года. Кроме того, появится поддержка и новых кабелей CopprLink. Так что на выход PCIe 6.0 на рынок стоит рассчитывать где-то в начале 2025 года. Конечно, хотелось бы привести цикл разработки PCI Express в соответствии с циклами других производителей, включая разработчиков Ethernet, Infiniband и CXL, но состав PCI-SIG, насчитывающий уже почти тысячу компаний-участников, продолжает расти, что, конечно, не способствует быстрому согласованию спецификаций и получению всех нужных образцов технологии. Более того, все устройства любого стандарта PCIe обязаны быть совместимы со старыми версиями, вплоть до 1.0. И весь этот процесс необходимо поддерживать и далее: на середину или конец 2025 года запланирован выпуск финальных спецификаций PCI Express 7.0. Так что FIY-фазы стоит ожидать не ранее 2028 года. При этом проверка устройств нового стандарта на взаимную совместимость, в том числе чисто электрическую, становится всё сложнее с учётом заявленных частот и скоростей и оттого всё более необходимой. Но даже с трёхлетним циклом разработки, говорит PCI-SIG, пока удаётся опережать требования индустрии. Пропускная способность I/O-систем тоже удваивается примерно каждые три года, но к этому моменту у разработчиков PCIe уже готов и протестирован новый стандарт, покрывающий все разумные потребности и массово реализуемый за разумные деньги. И сравнивать PCIe, например, с NVLink с этой точки зрения может быть не совсем корректно, поскольку целью PCI-SIG не является достижение предельно высокой производительности любой ценой. Вместо этого группа обеспечивает развитие разумной, совместимой экосистемы решений с наилучшим соотношением цены и возможностей. Это не означает, что в абсолютных значениях решения на базе новых стандартов будут дешевле, но, как отметил вице-президент, экосистема PCIe позволяет разработчикам выбрать приемлемое для каждого случая сочетание характеристик. В настоящее время спецификация PCIe 7.0 версии 0.5 стала доступна участникам PCI-SIG. Новый стандарт доводит скорость передачи данных до 128 ГТ/с на линию при повышении энергоэффективности. Напомним, начиная с PCIe 6.0 доступен режим кодирования Flit, позволяющий избежать накладных расходов при передаче данных, и сделан переход к модуляции PAM4. Оптический вариант PCIe 7.0 тоже появится, но всё ещё будет опциональным. По словам Соломона, разговоры о вынужденном переходе на «оптику» ведутся более десяти лет, но по факту возможностей «меди» всё ещё хватает и будет хватать.

01.05.2024 [17:00], Сергей Карасёв

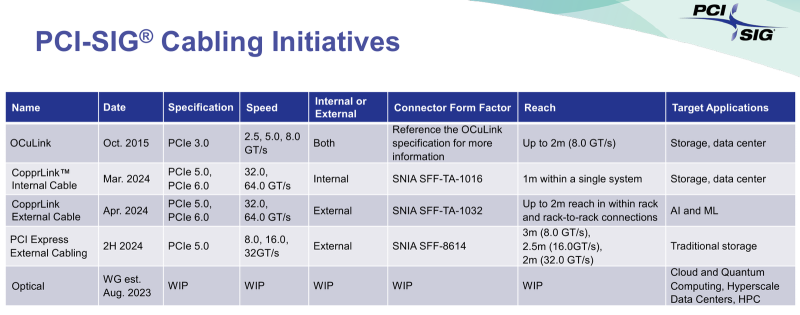

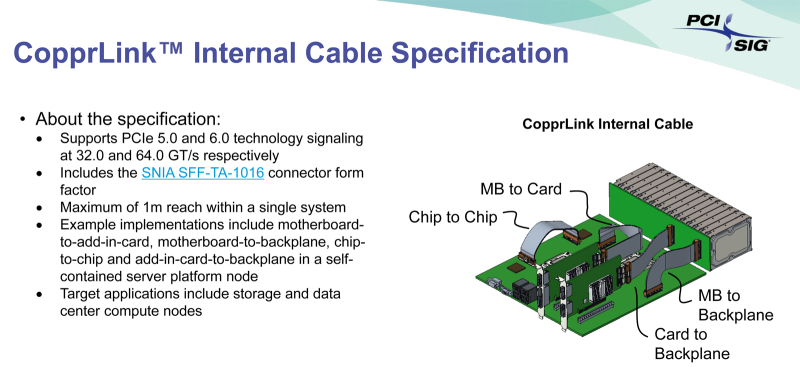

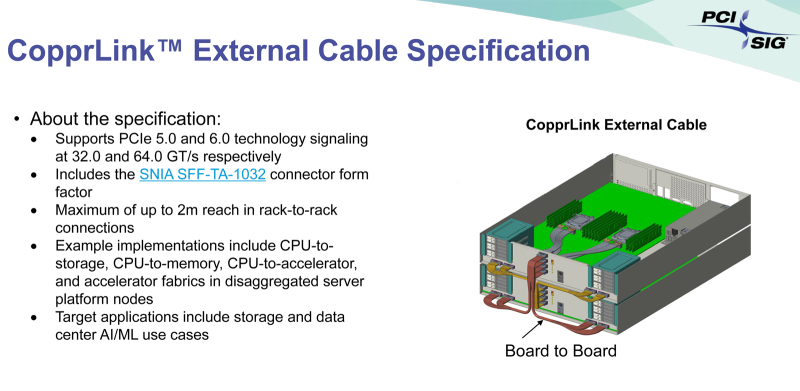

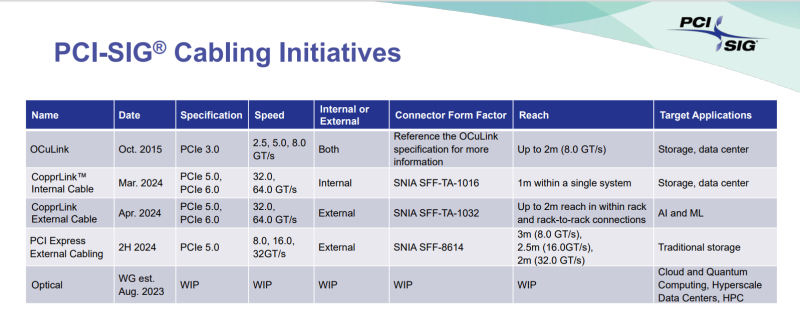

Внутри и снаружи: PCI-SIG обнародовала спецификации кабелей CopprLink для PCIe 5.0/6.0Организация PCI Special Interest Group (PCI-SIG) обнародовала спецификации электрических кабелей и разъёмов CopprLink для внешних и внутренних подключений PCIe 5.0/6.0. Новые соединения на основе меди позволят заменить существующие кабели OCuLink в тех случаях, когда требуется более высокая пропускная способность. Стандарт CopprLink был анонсирован в конце 2023 года. Кабели данного типа обеспечат высокоскоростные подключения в пределах отдельных систем, а также между различными узлами в составе стойки. Кроме того, как отмечалось ранее, разрабатываются варианты для межстоечного соединения. Спецификация CopprLink для внутренних подключений:

Спецификация CopprLink для внешних подключений:

Отмечается, что в дальнейшем кабели CopprLink будут развиваться с учётом возможностей интерфейса PCIe следующих поколений. Технология CopprLink, как ожидается, будет востребована в сферах, где необходимы небольшие задержки, включая дата-центры, производительные СХД, сети и пр. В будущем ожидается появление оптических кабелей PCIe.

14.03.2024 [23:45], Алексей Степин

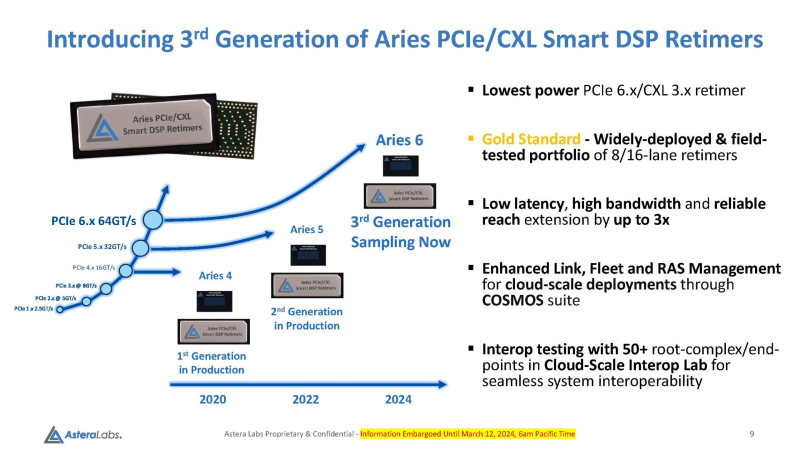

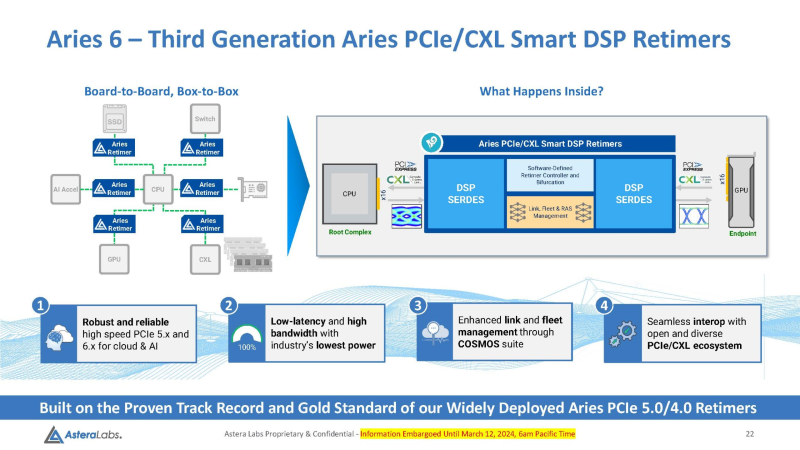

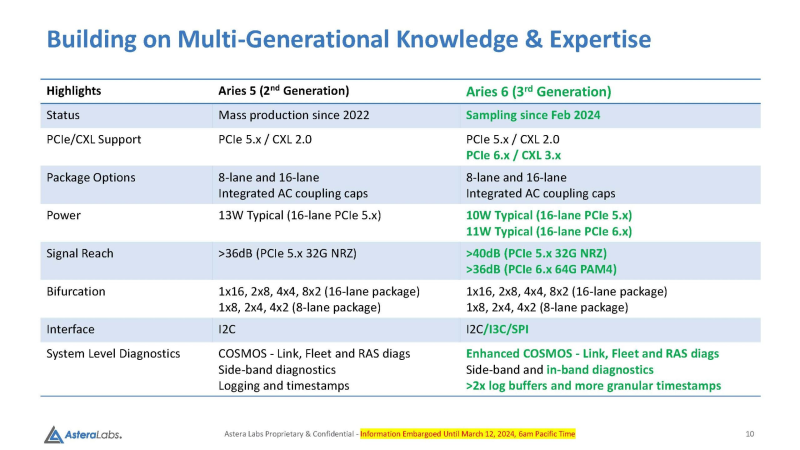

Войны ретаймеров: Astera Labs анонсировала чипы Aries 6 для PCIe 6.0Практически сразу после анонса чипов Broadcom Vantage 5 и 6 Astera представила свой вариант ретаймеров для инфраструктуры PCIe следующего поколения — серию чипов Aries 6, передаёт ServeTheHome. Высокий интерес к ретаймерам вызван теми возможностями, что открывает PCI Express 6.0 как в плане скоростей, так и в плане функциональности (CXL). А переход на новое поколение шины необходим для дальнейшего развития набирающего популярность генеративного ИИ. По мере роста скоростей PCI Express обострялась и проблема длины проводников на печатной плате, при которой сигнал достаточно устойчив и вписывается в окно требуемых характеристик. Если при переходе от PCIe 3.0 к 4.0 удалось обойтись сравнительно малой кровью, то для PCIe 5.0 уже потребовались более сложная схемотехника и более продвинутые ретаймеры. PCIe 6.0 же накладывает ещё более жёсткие требования к целостности сигнала. Платформы GPU-кластеров и СХД компактнее не становятся, так что требуемая длина проводников на печатных платах растёт, а вместе с ней растёт и важность ретаймеров, поскольку без них согласовать высокоскоростной сигнал PCIe 6.0 становится невозможно. Таким системам требуется сразу несколько подобных чипов, причём стоимость каждого из них достигает $20, так что суммарная стоимость этих компонентов на уровне целого ЦОД весьма внушительна. Новые чипы Aries 6 относятся к третьему поколению «умных» DSP-ретаймеров. Они представлены в вариантах с 8 и 16 линиями PCIe 6.0 и позволяют в три раза увеличить длину соответствующего соединения на плате, говорит Astera Labs. При этом новинки поддерживают CXL 3.x и предоставляют расширенные средства диагностики и управления COSMOS. Энергопотребление в режиме PCIe 6.0 при этом заявлено меньше, чем у Broadcom Vantage 6 — 11 Вт против 13 Вт у конкурента. Aries 6 уже протестированы на совместимость с полсотней разнообразных PCIe-соединений, включая root-комплексы и конечные устройства. И если Broadcom пока только говорит о ретаймерах для PCIe 6.0, а появление первого «кремния» Vantage 6 запланировано лишь на следующий год, то Astera Labs начала поставки образцов Aries 6 ещё в феврале. Похоже, Broadcom будет нелегко развернуться на этом рынке.

08.03.2024 [00:03], Алексей Степин

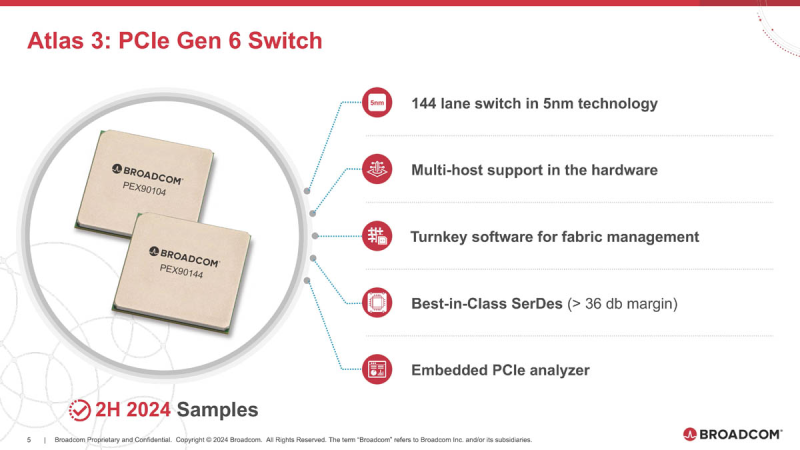

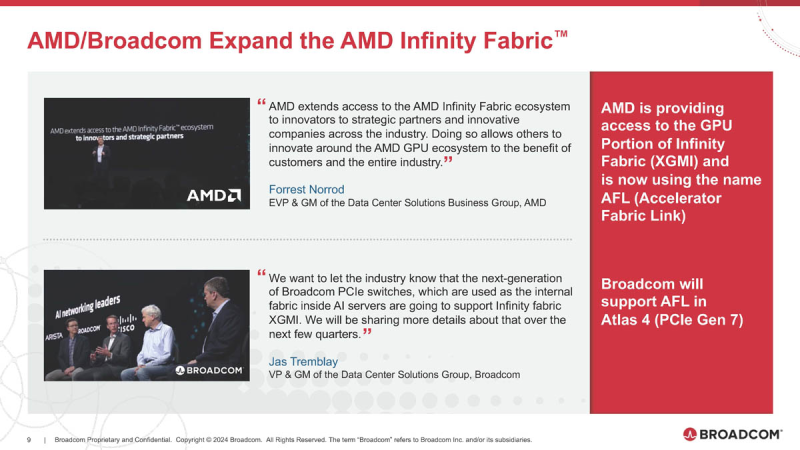

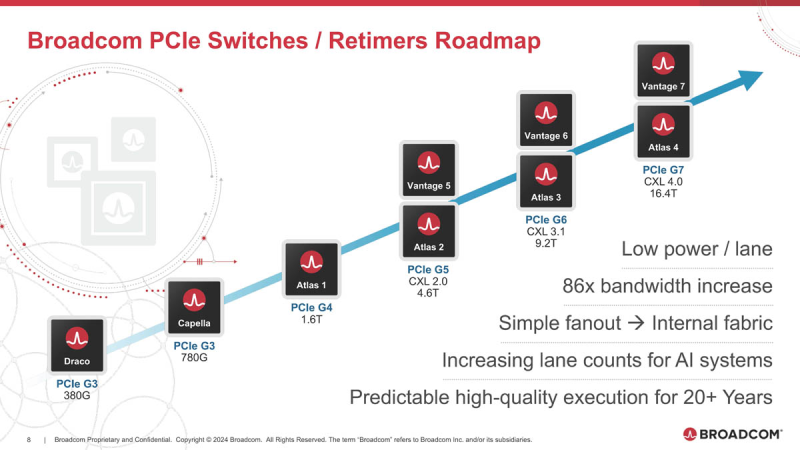

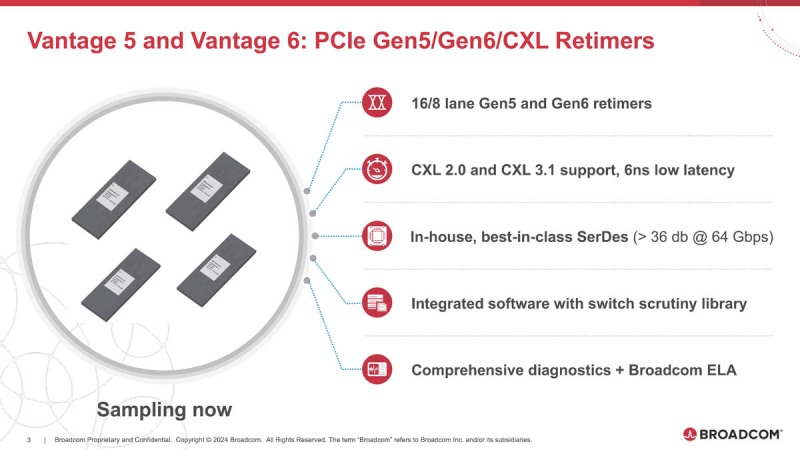

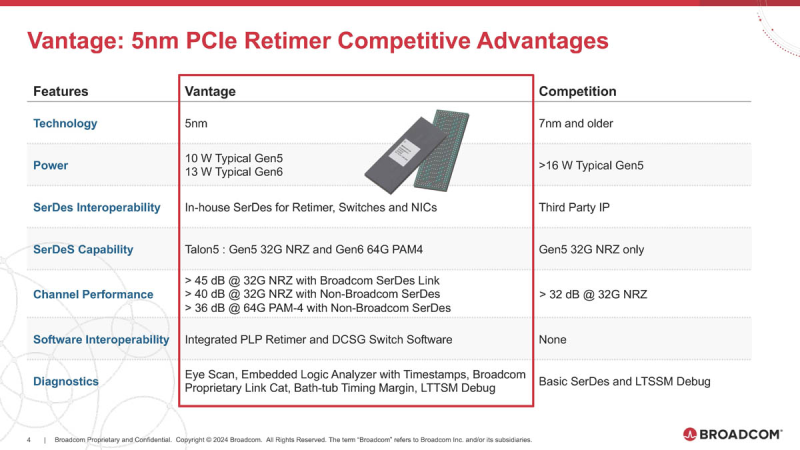

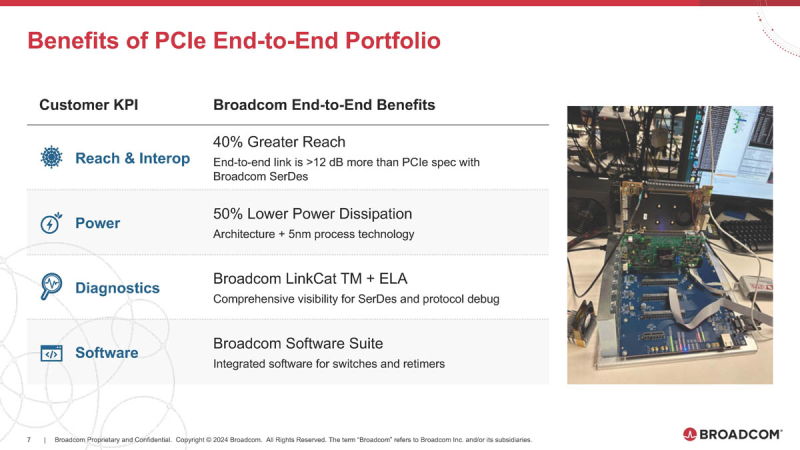

Broadcom готовит чипы для PCIe 6.0/7.0 с поддержкой AMD Infinity FabricОдним из столпов, на которых зиждется господство NVIDIA в мире ускорителей, является NVLink — высокоскоростной интерконнект, позволяющий чипам общаться напрямую не только в составе одного узла, но и за его пределами. AMD пытается ответить на это продвижением XGMI/Infinity Fabric, и в предварительном обзоре Instinct MI300 были затронуты вопросы топологии серверов в исполнении «красных». Ещё тогда, в момент анонса MI300, компания Broadcom объявила о поддержке данного интерконнекта в будущих поколениях своих PCIe-коммутаторов, а сейчас ресурс ServeTheHome поделился новыми подробностями. XGMI действительно станет коммутируемым, что упростит масштабирование систем на базе ускорителей AMD Instinct. Интерконнект получил официально название AFL (Accelerated Fabric Link). В основе AFL по-прежнему будет лежать PCI Express, в данном случае речь идёт уже о PCI Express 7.0. Поддержка данной технологии дебютирует в PCIe-коммутаторах Broadcom Atlas 4. В дополнение к ним будут выпущены и новые ретаймеры Vantage 7, которые также получат поддержку CXL 4.0. Но перед этим Broadcom начнёт поставки образцов чипов-коммутаторов Atlas 3 со 144 линиями PCIe 6.0 во II половине 2024 года, а серверы с такими коммутаторами появятся в 2025 году. Поддержка CXL здесь будет расширена до версии 3.1. Что касается ретаймеров, то здесь Broadcom уже нанесла ответный удар Astera Labs, анонсировав чипы серий Vantage 5 и Vantage 6 для экосистем PCI Express 5.0 и PCI Express 6.0 соответственно. Они будут выпускаться в вариантах с 8 и 16 линиями с опцией бифуркации и поддержкой CXL 2.0 и 3.1. Broadcom заявляет о более низком энергопотреблении, достигнутом за счёт применения 5-нм техпроцесса, лучших в индустрии блоках SerDes и расширенных средствах диагностики, интегрированных в новые ретаймеры. Экономичность здесь играет важную роль: хотя даже 7-нм ретаймер потребляет немного, таких микросхем в составе каждого GPU-сервера несколько, что при дальнейшем масштабировании выливается весьма серьёзные цифры. К тому же меньшая нагрузка ляжет и на систему охлаждения, ведь если CPU и ускорители могут обслуживаться СЖО, то остальные компоненты в таких серверах по-прежнему охлаждаются обычными вентиляторами. Что касается SerDes-блоков, то они позволят на 40 % удлинить соединения при сохранении стабильной работы. Ну а наличие продвинутого диагностического программного обеспечения с расширенными возможностями упростит разработку, отладку и ремонт систем нового поколения. Ретаймеры Vantage 5 будут использоваться в комплекте с коммутаторами Atlas 2 в решениях Broadcom уже сегодня, они обеспечат поддержку CXL 2.0, ну а системы с Vantage 6 и поддержкой CXL 3.1, как уже упоминалось, должны увидеть свет в следующем году. Astera Labs есть о чём беспокоиться: если на данный момент её ретаймерам почти нет альтернативы, то уже в ближайшем будущем ситуация может коренным образом измениться, поскольку Broadcom явно осознала всю важность этого компонента в экосистеме PCI Express и оценила солидный объём потенциальной клиентской базы.

13.10.2023 [00:45], Владимир Мироненко

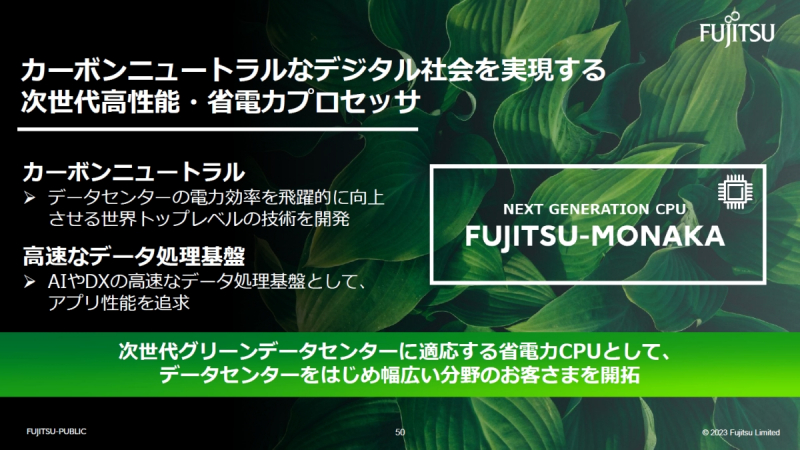

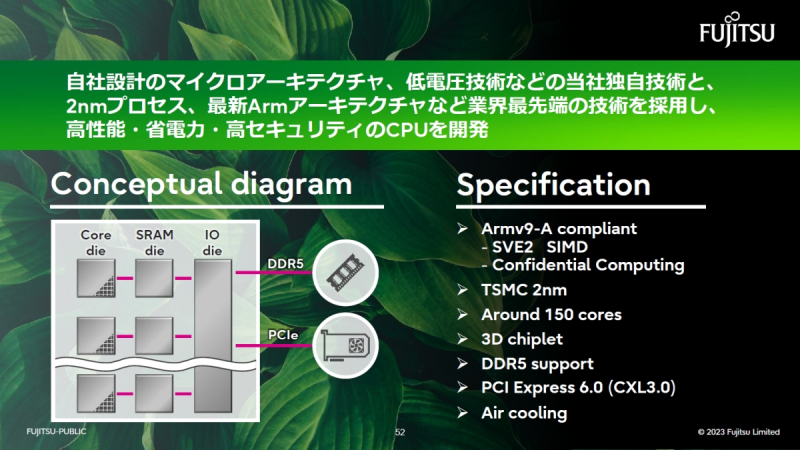

Fujitsu готовит 2-нм 150-ядерный серверный Arm-процессор MONAKA с поддержкой PCIe 6.0 и CXL 3.0Fujitsu провела на этой неделе брифинг для СМИ и аналитиков на заводе в Кавасаки, на котором рассказала о разработке серверного процессора MONAKA, появление которого на рынке запланировано в 2027 году, пишет ресурс MONOist. Впервые о создании нового поколения CPU компания объявила весной этого года, а часть средств на разработку выделило правительство Японии. Как сообщил Наоки Синдзё (Naoki Shinjo), гендиректор подразделения развития передовых технологий Fujitsu, MONAKA представляет собой высокопроизводительный энергоэффективынй процессор нового поколения, который разрабатывается для значительного повышения энергоэффективности ЦОД и обеспечения высокоскоростной обработки данных, необходимой для приложений ИИ и цифровой трансформации. MONAKA будет основан на процессорной архитектуре Arm с набором инструкций Armv9-A с поддержкой масштабируемых векторных расширений SVE2. Он будет представлять собой 3D-сборку из чиплетов, а и его изготовление будет осуществляться с использованием 2-нм техпроцесса TSMC. По словам Синдзё, у процессора будет около 150 ядер, поддержка памяти DDR5 и интерфейс PCIe 6.0 с CXL 3.0. При этом для работы ему будет достаточно воздушного охлаждения. Fujitsu ожидает, что MONAKA будет в два раза превосходить по энергоэффективности чипы конкурентов и во столько же раз опережать конкурентов по скорости обработки данных в области вычислений, ориентированных на рабочие нагрузки ИИ. За обеспечение безопасности данных в Armv9-A отвечает архитектура конфиденциальных вычислений Arm Confidential Compute Architecture (CCA). Также сообщается, что в суперкомпьютере-преемнике Fugaku, который будет запущен в 2030 году, будут использоваться процессоры, разработанные с применением технологий, задействованных в MONAKA. В отличие от узкоспециализированных HPC-процессоров FUjitsu A64FX, которые легли в основу Fugaku, чипы MONAKA являются более универсальными решениями.

26.10.2022 [12:43], Сергей Карасёв

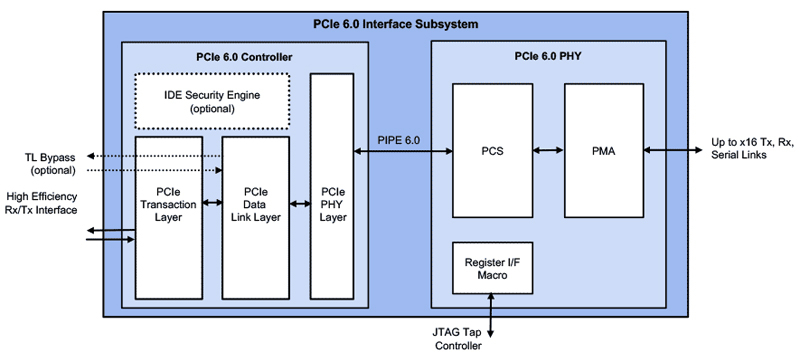

Rambus представила блоки PCIe 6.0 для серверных чиповКомпания Rambus сообщила о доступности своих решений PCI Express (PCIe) 6.0, которые ориентированы на серверные SoC, а также ИИ-чипы. Анонсированное решение включает микросхему PHY и контроллер. ИнтерфейсRambus PCIe 6.0, как утверждается, полностью оптимизирован для удовлетворения потребностей гетерогенных вычислительных архитектур. Упомянута поддержка CXL 3.0 и обратная совместимость с PCIe 5.0, 4.0 и 3.0/3.1. Контроллер Rambus PCIe 6.0 содержит движок IDE (Integrity and Data Encryption), который осуществляет мониторинг и защиту линий PCIe от физических атак. Реализованы различные механизмы для повышения эффективности работы интерфейса и технология коррекции ошибок FEC. Полная поддержка CXL 3.0 на стороне PHY обеспечивает улучшенные возможности по работе с пулами памяти, продвинутые режимы когерентности, а также многоуровневую коммутацию.

Источник изображения: Rambus «Быстрое развитие ИИ, машинного обучения и нагрузок с интенсивным использованием данных стимулирует непрерывную эволюцию архитектур ЦОД, для которых необходима всё более высокая производительность. Подсистема Rambus PCIe 6.0 способна удовлетворить потребности дата-центров следующего поколения в плане задержек, мощности, занимаемой площади и безопасности», — заявляет Rambus. |

|