Материалы по тегу: cxl

|

13.09.2023 [14:57], Сергей Карасёв

Разработчик CXL-платформы для ИИ Enfabrica получил $125 млн финансированияСтартап Enfabrica, специализирующийся на разработке инфраструктурных решений в сфере ИИ, по сообщению ресурса SiliconAngle, провёл крупный раунд финансирования Series B и привлёк $125 млн. Enfabrica, основанная в 2020 году, вышла из режима скрытности в начале 2023-го на фоне ИИ-бума. Раунд Series B проводится под руководством Atreides Management с участием Sutter Hill Ventures, IAG Capital Partners, Liberty Global Ventures, NVIDIA, Valor Equity Partners и Alumni Ventures. Стартап заявляет, что его технологии могут помочь в решении критически важных проблем ввода-вывода и масштабирования памяти, которые становятся все более актуальными по мере стремительного роста размера ИИ-моделей. Enfabrica предлагает CXL-платформу Accelerated Compute Fabric (ACF) на базе ASIC собственной разработки. Платформа позволяет напрямую подключать другу к другу любую комбинацию GPU, CPU, DDR5 CXL и SSD, а также предоставляет 800GbE-интерконнект.

Источник изображения: Enfabrica Утверждается, что заказчики могут сократить затраты на вычисления до 50 % при работе с большими языковыми моделями (LLM) и до 75 % в случае рекомендательных систем на основе машинного обучения. В целом, заказчикам обещаны двукратное увеличение производительности на доллар, повышение пропускной способности в 10 раз по сравнению со стандартными сетевыми картами и четырёхкратное улучшение производительности на ватт затрачиваемой энергии.

27.08.2023 [11:22], Сергей Карасёв

H3C и Montage объединили усилия с целью развития технологии CXLКитайская корпорация New H3C Group (H3C), специализирующаяся на выпуске серверов и другого оборудования корпоративного класса, и компания Montage Technology сообщили о заключении соглашения о стратегическом сотрудничестве. Оно распространяется на технологию Compute Express Link (CXL) и другие инновационные разработки. Напомним, CXL — высокоскоростной интерконнект, отвечающий за взаимодействие хост-процессора с акселераторами, буферами памяти, умными устройствами ввода/вывода и пр. В основе CXL лежат физический и электрический интерфейсы PCIe.

Источник изображения: H3C По условиям договора, H3C Group будет использовать процессоры Montage Jintide в своих вычислительных платформах, СХД, сетевых устройствах и системах обеспечения безопасности. В этих чипах реализованы технологии PrC и DSC, которые обеспечивают различные уровни аппаратной защиты. Кроме того, Montage одной из первых в мире представила CXL-решения. Стороны намерены совместно вести исследования в области передовых технологий, а также разрабатывать более экономичные серверные продукты с улучшенными вычислительными возможностями и решения общего назначения с конвергентной вычислительной архитектурой. В совместном заявлении H3C и Montage Technology говорится, что договор станет новой отправной точкой для компаний в достижении взаимовыгодного сотрудничества. Стороны намерены интегрировать свои существующие наработки, ресурсы и технологии для ускорения создания и вывода на рынок передовых продуктов, отвечающих потребностям различных отраслей промышленности.

24.03.2023 [20:28], Алексей Степин

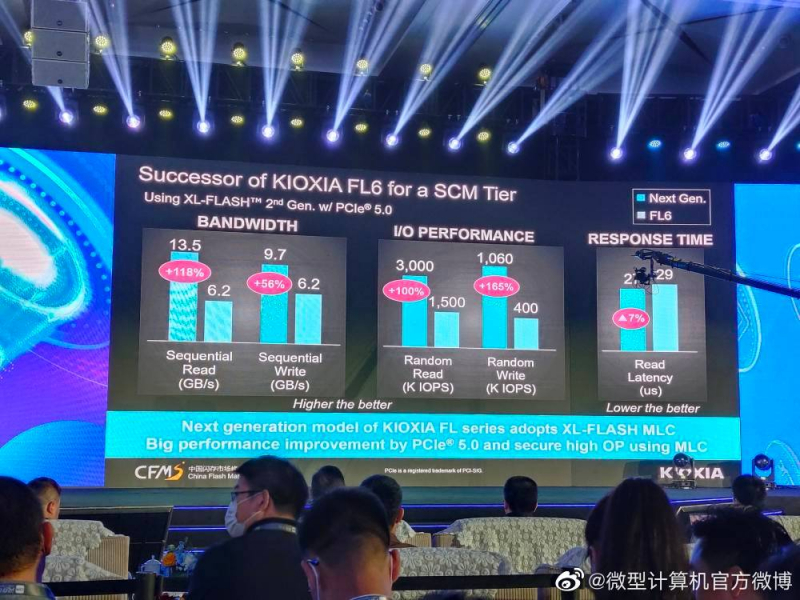

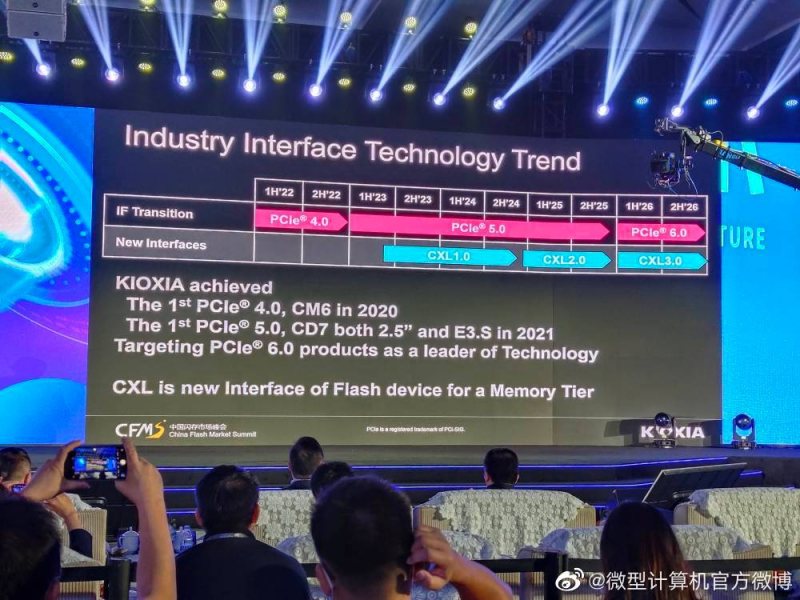

Kioxia анонсировала серверные SSD на базе XL-FLASH второго поколенияПо мере внедрения новых версий PCI Express растут и линейные скорости SSD. Не столь давно 3-4 Гбайт/с было рекордно высоким показателем, но разработчики уже штурмуют вершины за пределами 10 Гбайт/с. Компания Kioxia, крупный производитель флеш-памяти и устройств на её основе, объявила на конференции 2023 China Flash Market о новом поколении серверных накопителей, способных читать данные со скоростью 13,5 Гбайт/с. Новые высокоскоростные SSD будут построены на базе технологии XL-FLASH второго поколения. Первое поколение этих чипов компания (тогда Toshiba) представила ещё в 2019 году. В основе лежат наработки по BiCS 3D в однобитовом варианте, что позволяет устройствам на базе этой памяти занимать нишу Storage Class Memory (SCM) и служить заменой ушедшей с рынка технологии Intel Optane. Как уже сообщалось ранее, XL-FLASH второго поколения использует двухбитовый режим MLC, но в любом случае новые SSD Kioxia в полной мере раскроют потенциал PCI Express 5.0. Они не только смогут читать данные на скорости 13,5 Гбайт/с и записывать их на скорости 9,7 Гбайт/с, но и обеспечат высокую производительность на случайных операциях: до 3 млн IOPS при чтении и 1,06 млн IOPS при записи. Время отклика для операций чтения заявлено на уровне 27 мкс, против 29 мкс у XL-FLASH первого поколения. Kioxia полагает, что PCI Express 5.0 и CXL 1.x станут стандартами для серверных флеш-платформ класса SCM надолго — господство этих интерфейсов продлится минимум до конца 2025 года, лишь в 2026 году следует ожидать появления первых решений с поддержкой PCI Express 6.0. Активный переход на более новую версию CXL ожидается в течение 2025 года. Пока неизвестно, как планирует ответить на активность Kioxia другой крупный производитель флеш-памяти, Samsung Electronics, которая также располагает высокопроизводительной разновидностью NAND под названием Z-NAND.

02.08.2022 [16:00], Алексей Степин

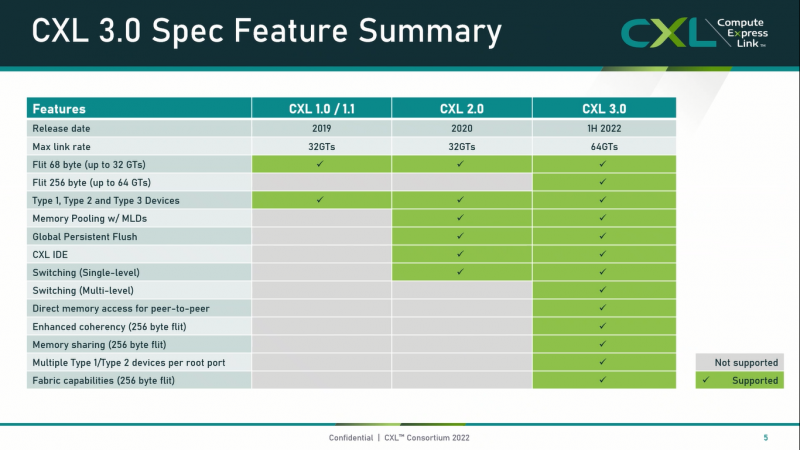

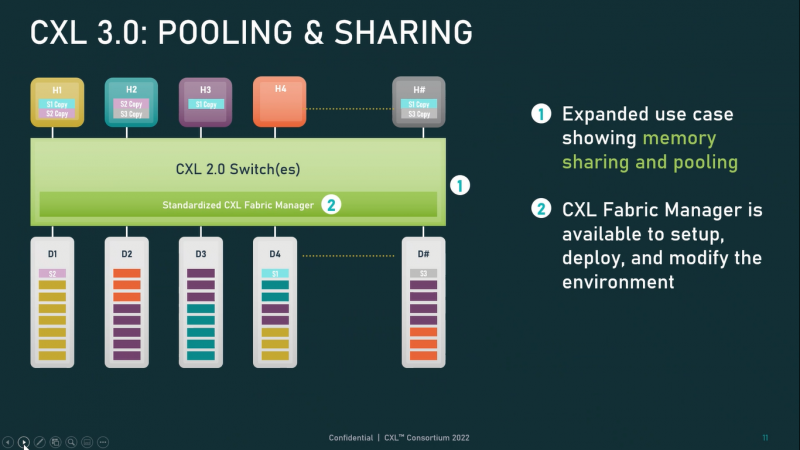

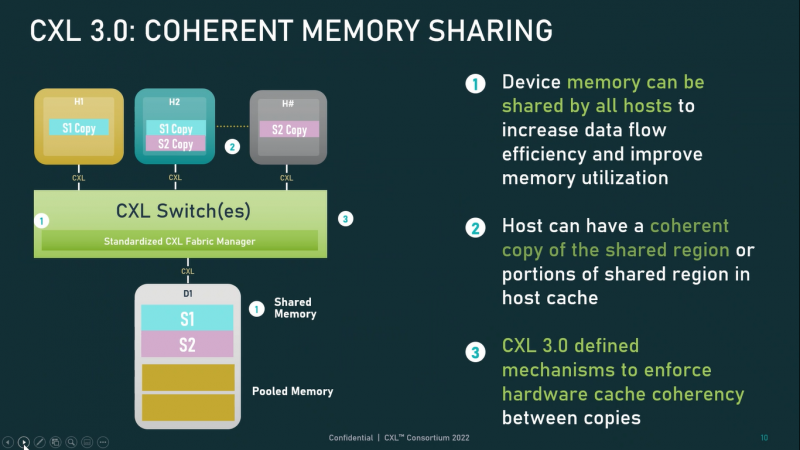

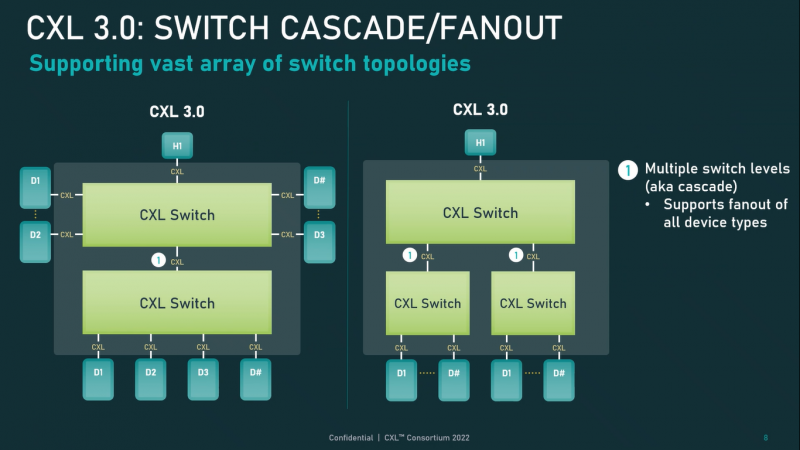

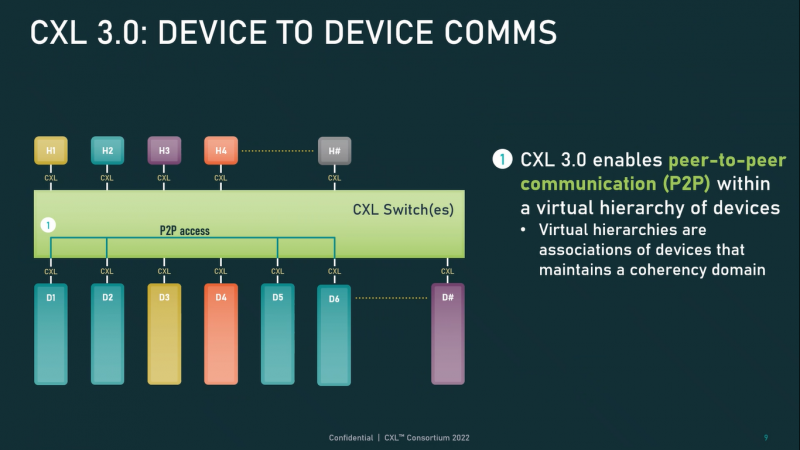

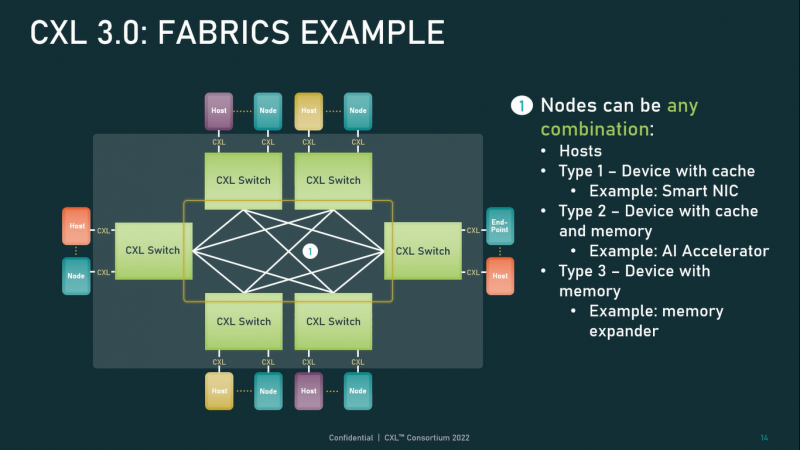

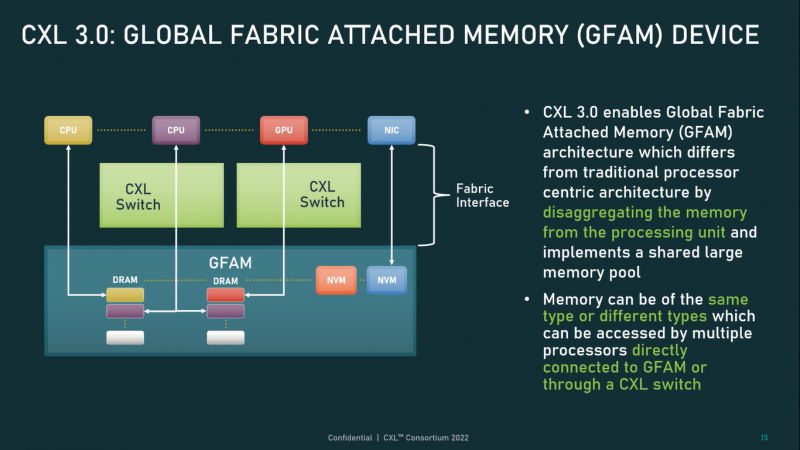

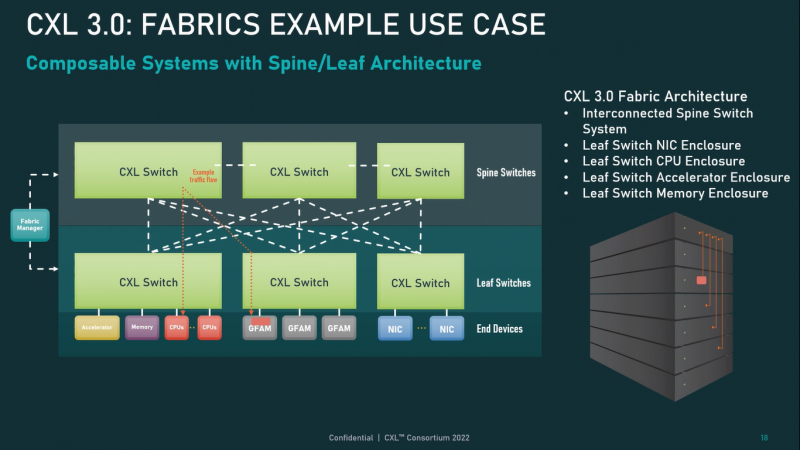

Опубликованы спецификации Compute Express Link 3.0Мало-помалу стандарт Compute Express Link пробивает себе путь на рынок: хотя процессоров с поддержкой ещё нет, многие из элементов инфраструктуры для нового интерконнекта и базирующихся на нём концепций уже готово — в частности, регулярно демонстрируются новые контроллеры и модули памяти. Но развивается и сам стандарт. В версии 1.1, спецификации на которую были опубликованы ещё в 2019 году, были только заложены основы. Но уже в версии 2.0 CXL получил массу нововведений, позволяющих говорить не просто о новой шине, но о целой концепции и смене подхода к архитектуре серверов. А сейчас консорциум, ответственный за разработку стандарта, опубликовал свежие спецификации версии 3.0, ещё более расширяющие возможности CXL. И не только расширяющие: в версии 3.0 новый стандарт получил поддержку скорости 64 ГТ/с, при этом без повышения задержки. Что неудивительно, поскольку в основе лежит стандарт PCIe 6.0. Но основные усилия разработчиков были сконцентрированы на дальнейшем развитии идей дезагрегации ресурсов и создания компонуемой инфраструктуры. Сама фабрика CXL 3.0 теперь допускает создание и подключение «многоголовых» (multi-headed) устройств, расширены возможности по управлению фабрикой, улучшена поддержка пулов памяти, введены продвинутые режимы когерентности, а также появилась поддержка многоуровневой коммутации. При этом CXL 3.0 сохранил обратную совместимость со всеми предыдущими версиями — 2.0, 1.1 и даже 1.0. В этом случае часть имеющихся функций попросту не будет активирована. Одно из ключевых новшеств — многоуровневая коммутация. Теперь топология фабрики CXL 3.0 может быть практически любой, от линейной до каскадной с группами коммутаторов, подключенных к коммутаторам более высокого уровня. При этом каждый корневой порт процессора поддерживает одновременное подключение через коммутатор устройств различных типов в любой комбинации. Ещё одним интересным нововведением стала поддержка прямого доступа к памяти типа peer-to-peer (P2P). Проще говоря, несколько ускорителей, расположенных, к примеру, в соседних стойках, смогут напрямую общаться друг с другом, не затрагивая хост-процессоры. Во всех случаях обеспечивается защита доступа и безопасность коммуникаций. Кроме того, есть возможность разделить память каждого устройства на 16 независимых сегментов. При этом поддерживается иерархическая организация групп, внутри которых обеспечивается когерентность содержимого памяти и кешей (предусмотрена инвалидация). Теперь помимо эксклюзивного доступа к памяти из пула доступен и общий доступ сразу нескольких хостов к одному блоку памяти, причём с аппаратной поддержкой когерентности. Организация пулов теперь не отдаётся на откуп стороннему ПО, а осуществляется посредством стандартизированного менеджера фабрики. Сочетание новых возможностей выводит идею разделения памяти и вычислительных ресурсов на новый уровень: теперь возможно построение систем, где единый пул подключенной к фабрике CXL 3.0 памяти (Global Fabric Attached Memory, GFAM) действительно существует отдельно от вычислительных модулей. При этом возможность адресовать до 4096 точек подключения скорее упрётся в физические лимиты фабрики. Пул может содержать разные типы памяти — DRAM, NAND, SCM — и подключаться к вычислительным мощностями как напрямую, так и через коммутаторы CXL. Предусмотрен механизм сообщения самими устройствами об их типе, возможностях и прочих характеристиках. Подобная архитектура обещает стать востребованной в мире машинного обучения, в котором наборы данных для нейросетей нового поколения достигают уже поистине гигантских размеров. В настоящее время группа CXL уже включает 206 участников, в число которых входят компании Intel, Arm, AMD, IBM, NVIDIA, Huawei, крупные облачные провайдеры, включая Microsoft, Alibaba Group, Google и Meta✴, а также ряд крупных производителей серверного оборудования, в том числе, HPE и Dell EMC.

01.08.2022 [23:00], Игорь Осколков

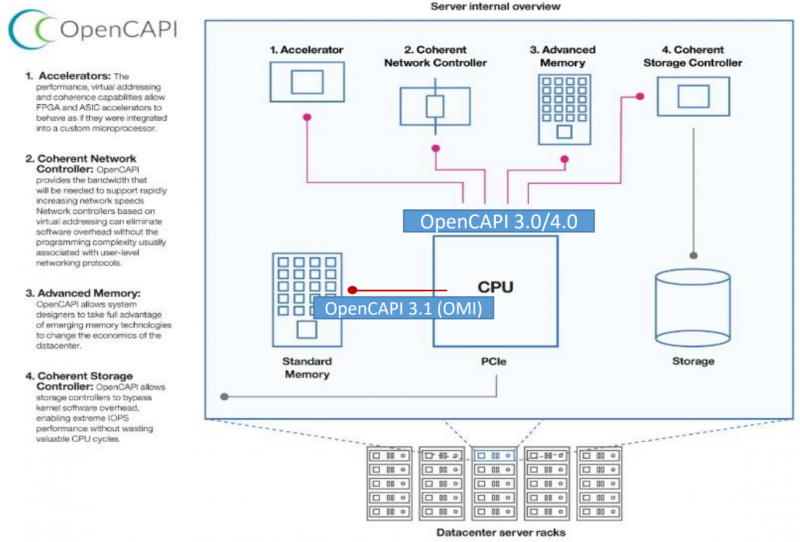

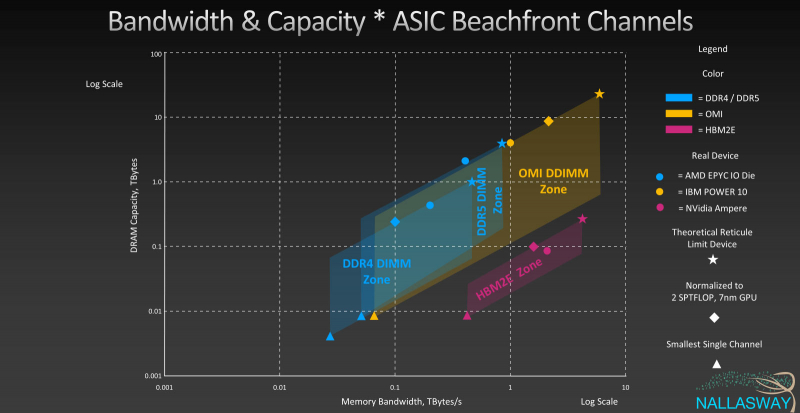

Великое объединение: спецификации и наработки OpenCAPI и OMI планируется передать консорциуму CXLКонсорциумы OpenCAPI Consortium (OCC) и Compute Express Link (CXL) подписали соглашение, которое подразумевает передачу в пользу CXL всех наработок и спецификаций OpenCAPI и OMI. Если будет получено одобрения всех участвующих сторон, то это будет ещё один шаг в сторону унификации ключевых системных интерфейсов и возможности реализации новых архитектурных решений. Во всяком случае, на бумаге. Консорциумы OpenCAPI (Open Coherent Accelerator Processor Interface) был сформирован в 2016 году с целью создание единого, универсального, скоростного и согласованного интерфейса для связи CPU с ускорителями, сетевыми адаптерами, памятью, контроллерами и устройствами хранения и т.д. Причём в независимости от типа и архитектуры самого CPU. На тот момент новый интерфейс был определённо лучше распространённого тогда PCIe 3.0. С течением времени дела у OpenCAPI шли ни шатко ни валко, однако фактически его использование было ограничено только POWER-платформами от IBM. Тем не менее, в недрах OpenCAPI родился ещё один очень интересный стандарт — Open Memory Interface (OMI). OMI, если коротко, предлагает некоторую дезагрегацию путём добавления буферной прослойки между CPU и RAM. С одной стороны у OMI есть унифицированный последовательный интерфейс для подключения к CPU, с другой — интерфейсы для подключения какой угодно памяти, на выбор конкретного производителя. OMI позволяет поднять пропускную способность памяти, не раздувая число контактов и физические размеры и самого CPU, и модулей. Однако и в данном случае массовая поддержка OMI по факту есть только в процессорах IBM POWER10. Концептуально CXL в части работы с памятью повторяет идею OMI, только в данном случае в качестве физического интерфейса используется распространённый PCIe. Существенная разница c OMI в том, что начальная поддержка CXL будет в грядущих процессорах AMD и Intel. А Samsung и SK Hynix уже готовят соответствующие DDR5-модули. Да и в целом поддержка CXL в индустрии намного шире. Так что консорциуму CXL, по-видимому, осталось поглотить только ещё один конкурирующий стандарт в лице CCIX, как это уже произошло с Gen-Z. Комментируя соглашение, президент консорциума CXL отметил, что сейчас наиболее удачное время для объединения усилий, которое принесёт пользу всей IT-индустрии. Участники OpenCAPI имеют богатый опыт, который поможет улучшить грядущие спецификации CXL и избежать ошибок.

03.04.2020 [13:37], Геннадий Детинич

Консорциумы CXL и Gen-Z объединяют усилия: протоколы станут совместимыми, а возможности расширятсяКонсорциумы CXL и Gen-Z сообщили, что их руководящие органы подписали договор о взаимопонимании. Пописанный меморандум раскрывает планы сотрудничества между двумя организациями, обещая совместимые протоколы и расширенные возможности каждого из представленных интерфейсов. Первые версии спецификаций Gen-Z и CXL (Compute Express Link) вышли, соответственно, в феврале 2018 года и в марте 2019 года. Каждый из этих интерфейсов призван обойти ограничения по пропускной способности, накладываемые на многоядерные и многоузловые конфигурации процессоров и ускорителей.  Как один, так и другой интерфейс отвечают за согласованность кешей множества подключённых решений и обеспечивают минимальные задержки при доступе к вычислительным ресурсам и хранилищам данных на основе ОЗУ или долговременных накопителей. В то же время интерфейс CXL специализируется на согласованной работе внутри шасси, а интерфейс Gen-Z позволяет согласовывать работу на уровне блоков, стоек и массивов. В целом, участники консорциума Gen-Z поддержали идею Compute Express Link и признали её как дополняющую для развития интерфейса Gen-Z. В течение прошлого года в консорциум CXL, за организацией которого стоит компания Intel, вошли много компаний, включая AMD и ARM. Дело оставалось за малым ― объединить усилия и добиться совместимости протоколов и архитектур.  Сегодня такой день настал. Консорциумы CXL и Gen-Z договорились организовать совместные смешанные рабочие группы для разработки «мостов» между протоколами обеих спецификаций и сделать всё необходимое, чтобы расширить возможности каждого из стандартов за счёт возможностей другого. |

|