Материалы по тегу: akeana

|

16.08.2024 [09:20], Алексей Степин

От IoT до ЦОД: Akeana, основанная выходцами из Marvell, представила три семейства ядер RISC-VВ 2021 году выходцы из Marvell и Cavium, стоявшие в своё время за созданием серверных Arm-процессоров ThunderX, основали стартап Akeana, который на днях вышел из т.н. скрытого режима и анонсировал RISC-V ядра собственной разработки. Akeana прямо говорит, что планирует бросить вызов Arm, SiFive, Andes и другим разработчикам чипов с архитектурой RISC-V. За три года Akeana удалось получить от крупных инвесторов, включая Kleiner Perkins, Mayfield и Fidelity, финансирование свыше $100 млн. А на этой неделе Akeana представила целую серию кастомизируемых IP-решений, в том числе три дизайна процессорных ядер с архитектурой RISC-V.

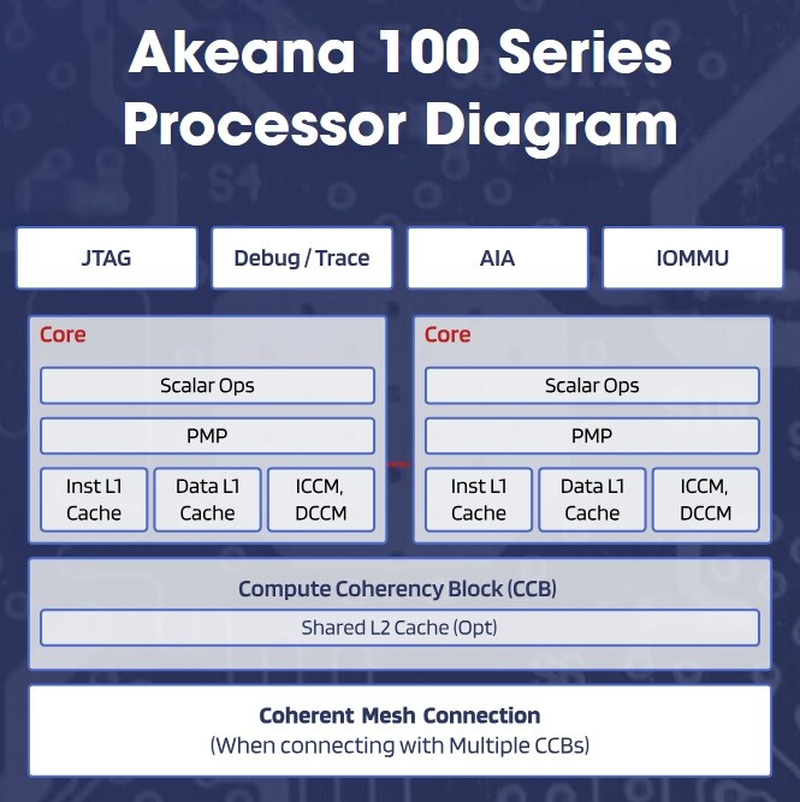

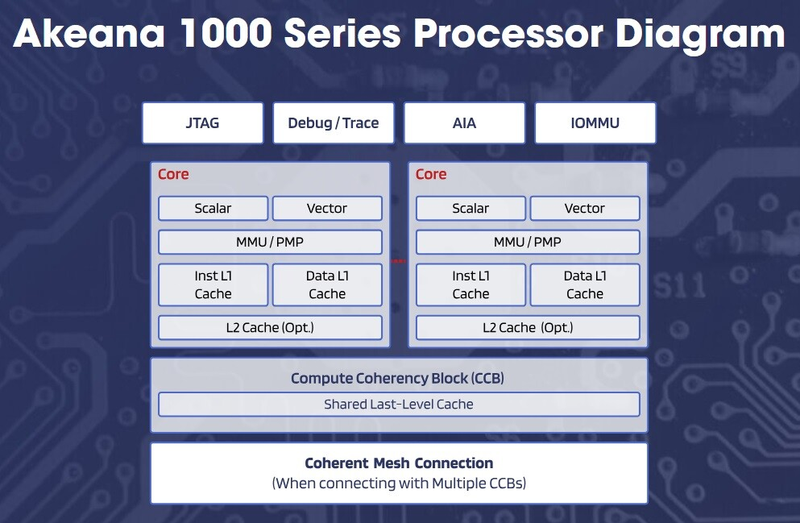

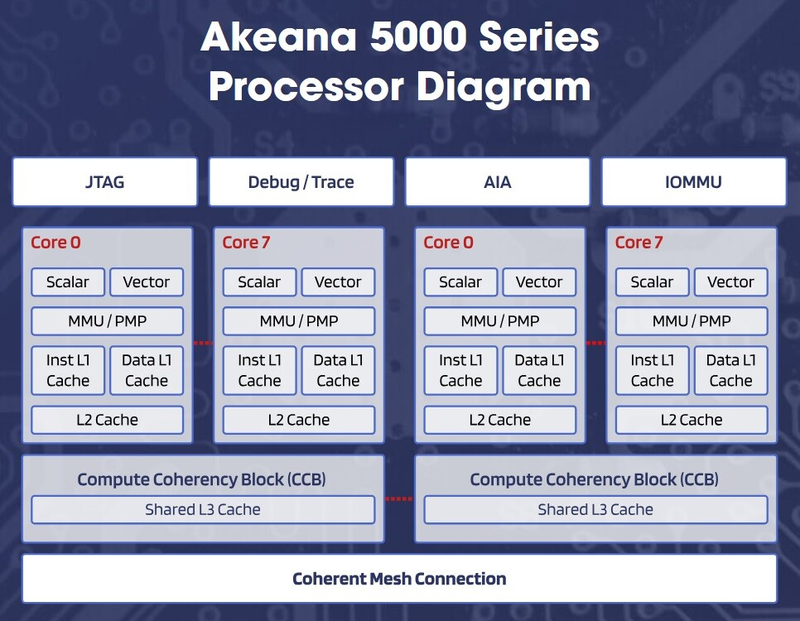

Источник здесь и далее: Akeana Остальные решения относятся к экосистеме, которую планирует сформировать Akeana. Это система высокоскоростного интерконнекта SCI (Scalable Coherent Interconnect, совместим с AMBA CHI), блоки контроллера прерываний, IOMMU, систему кластеризации и когерентности кешей, блоки векторных и матричных вычислений для ИИ-нагрузок и многое другое, включая разнообразные микроконтроллеры и подсистемы.  Что касается процессорных дизайнов, то компания представила сразу три серии:

В каждой из серий анонсировано по три-четыре базовых варианта с разной функциональностью, конфигурацией и объёмами кешей. Наибольший интерес представляет, пожалуй, серия 5000, которая позиционируется в качестве достаточно мощных процессоров для использования как в ПК и ноутбуках (в последнем случае предлагается использовать гетерогенный вариант с Akeana 1000 в качестве «малых» ядер), так и в качестве серверной инфраструктурной основы.  Ядра Akeana поддерживают кластеризацию (до 8 ядер на кластер), но, к сожалению, компания пока не раскрывает пределов масштабирования, тогда как новый дизайн SiFive, как мы уже знаем, позволяет создавать процессоры с числом ядер до 256. Говорить о каких-то реальных прототипах ещё рано, но все три серии ядер Akeana уже доступны для лицензирования клиентами. Очевидно, что экосистема RISC-V вступает в фазу активного развития: одна за другой компании-разработчики представляют всё новые и новые дизайны процессорных ядер и целых платформ, причём в широчайшем диапазоне характеристик — от экономичных микроконтроллеров до многоядерных серверных решений. |

|